# Device Physics and Architecture Advances in Tunnel Field-Effect Transistors

Zehan Wu | Yifei Zhao | Fumei Yang | Jianhua Hao

Department of Applied Physics, The Hong Kong Polytechnic University, Hung Hom, Hong Kong, People's Republic of China

**Correspondence:** Jianhua Hao ([jh.hao@polyu.edu.hk](mailto:jh.hao@polyu.edu.hk))

**Received:** 28 April 2025 | **Revised:** 26 June 2025 | **Accepted:** 3 August 2025

**Funding:** This study was supported by the Research Grants Council of Hong Kong (RGC GRF No. 15304224, PolyU SRFS2122-5S02, AoE/P-701/20), and PolyU Project of 1-YWBG and RCNN 1-CEOH.

**Keywords:** beyond CMOS devices | subthreshold swing device physics | three-dimensional nanowire | tunnel field-effect transistor | two-dimensional material | van der Waals heterostructure

## ABSTRACT

The persistent pursuit of miniaturization and energy efficiency in semiconductor technology has driven the scaling of complementary metal-oxide-semiconductor field-effect transistors (CMOS FETs, i.e., the MOSFETs) to their physical limits. Conventional MOSFETs face intrinsic challenges, especially the Boltzmann limit that imposes a fundamental lower bound on the subthreshold swing ( $SS \geq 60 \text{ mV dec}^{-1}$  at room temperature). This limitation severely restricts voltage scaling and exacerbates static power dissipation. To overcome these bottlenecks, tunnel field-effect transistors (TFETs) have emerged as a promising post-CMOS alternative. The advantages of ultra-small  $SS$  well below the Boltzmann limit, as well as ultralow leakage currents, make TFETs ideal for low-power electronics and energy-efficient computing in the future information industry. However, its current development has encountered significant resistance to further performance improvement requirements; new breakthroughs have evolved to be based on interdisciplinary research that covers materials science, device technology, theoretical physics, and so on. Here, we provide a review on the design and development of TFET, which mainly describes the device physics model of tunnel junctions, and discusses the optimization direction of key parameters, the design direction of potential structures, and the development direction of the innovation system based on the device physics. Also, we visualize the framework for the figures of merit of TFET performance and further forecast the future applications of TFET.

## 1 | Introduction

### 1.1 | Fundamental Limitations Driving Beyond-CMOS Innovation

The evolution of conventional MOSFET technology has historically followed Moore's Law and Dennard scaling principles, achieving exponential performance improvements through dimensional scaling and supply voltage reduction. Over the past two decades, three key parameters—gate length, gate medium thickness, and junction depth—have all shrunk by about three orders of magnitude [1]. This technological breakthrough not

only reflects the rapid development of the manufacturing process, but also directly promotes the substantial improvement of the power performance index. As Moore's Law continues to advance, chip manufacturers continue to reduce the size to improve integration and efficiency by optimizing transistor structures. For example, modern fin-type field-effect transistors (FinFETs), fully-depleted silicon-on-insulator (FD-SOI), and nanosheet transistors, are designed in response to this trend, which can effectively reduce leakage current and increase switching speed, thus achieving higher energy efficiency. In addition, advances in the field of materials science have also provided important support for these achievements, such as the

This is an open access article under the terms of the [Creative Commons Attribution](#) License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

© 2025 The Author(s). *Interdisciplinary Materials* published by Wuhan University of Technology and John Wiley & Sons Australia, Ltd.

application of high dielectric constant materials that allow the gate dielectric layer to be thinner while still maintaining good insulation properties. In short, the rapid development of information technology depends on the joint advancement of interdisciplinary, including electrical and electronics, materials, theoretical physics, and even economics. These interdisciplinary research and development have jointly promoted the performance evolution and application development of commercial electronic equipment, laying a solid foundation for a more advanced information society in the future.

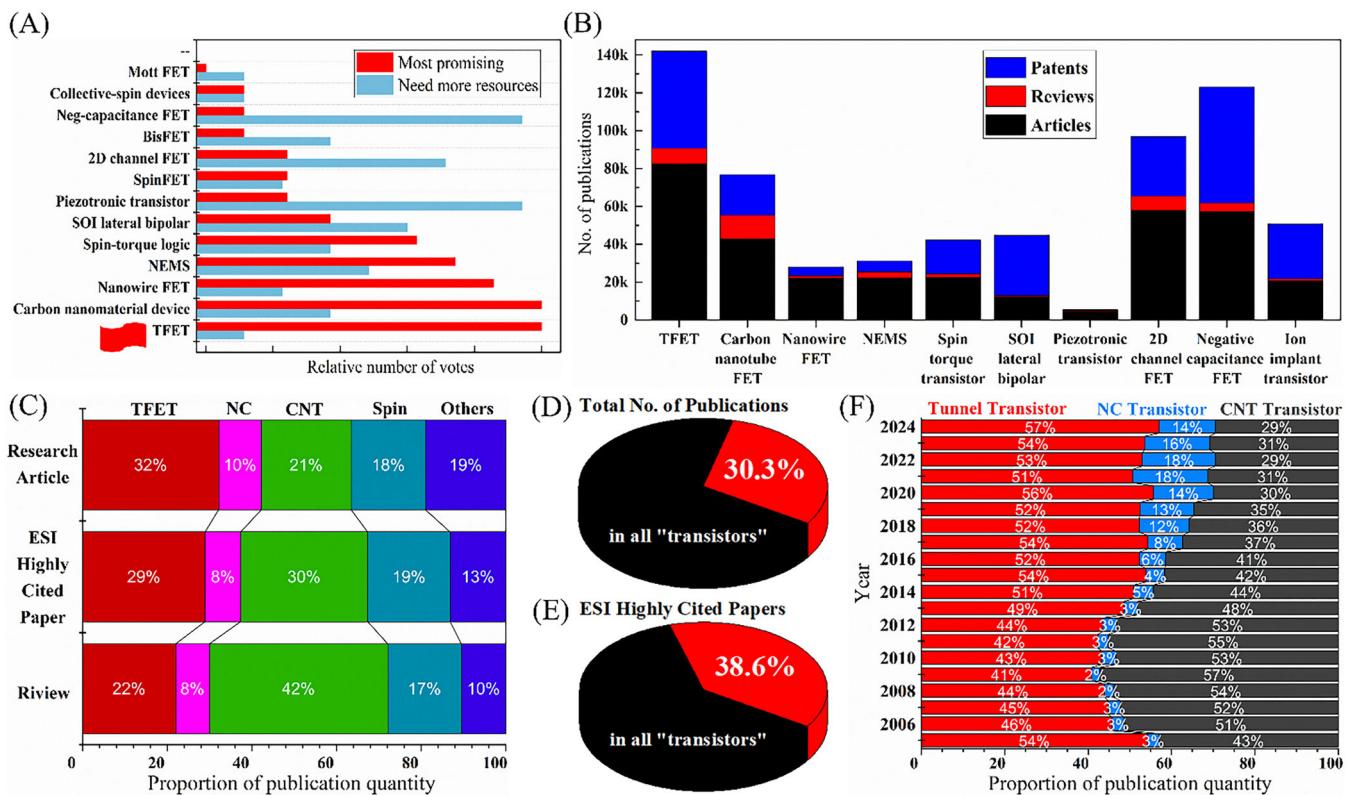

Most recently, although the iteration rate of commercial electronic devices is still fast, the impetus to continuously shrink in device dimension and power has been insufficient. Specifically, as device dimensions approach the sub-10 nm regime, three fundamental physical limitations have emerged. The first one is the power density crisis. At 5 nm technology nodes, static power dissipation from gate leakage and subthreshold conduction accounts for >40% of total power consumption. The International Roadmap for Devices and Systems (IRDS) projects that conventional CMOS scaling will lead to untenable power densities exceeding 500 W/cm<sup>2</sup> by 2030 [2]. Secondly, the short-channel effects (SCEs) proliferation is becoming a serious hindrance. Quantum tunneling through ultrathin gate dielectrics and drain-induced barrier lowering (DIBL) degrade switching characteristics, specifically the OFF-state current ( $I_{OFF}$ ). For gate lengths below 12 nm, DIBL coefficients exceed 100 mV<sup>-1</sup>, causing unacceptable threshold voltage roll-off. The most direct way to solve these two problems is to continuously lower the supply voltage ( $V_{DD}$ ); However, the third wall appears, and that is the thermodynamic barrier to subthreshold swing in MOSFET. In many studies, this wall has been described as “Boltzmann’s tyranny” of thermionic emission, which mandates a minimum SS of 60 mV dec<sup>-1</sup> at room temperature (RT) [3, 4]. This creates an exponential relationship between  $I_{OFF}$  and threshold voltage ( $V_{TH}$ ), fundamentally limits MOSFET switching characteristics and severely constraining voltage scaling in advanced technology nodes. Therefore, the research for a steep slope transistor that can achieve RT SS well below 60 mV dec<sup>-1</sup> has become the most critical pass to continue the Dennard scaling principles and Moore’s Law; and specifically, the IRDS 2023 Edition has identified TFETs as the most promising “beyond CMOS” logic device with energy advantages that “moving close to the target” (Figure 1A).

## 1.2 | Development and Advantages of TFET Technology

The concept of band-to-band tunneling (BTBT) in semiconductor was proposed in the 1960s [5]. Early theoretical models established the SS advantage through Wentzel-Kramers-Brillouin (WKB) approximation [6]; Subsequently, a considerable amount of research on the subthreshold swing device physics has been deeply promoted. Further, the upsurge of research began with the experimental carbon nanotube TFET reported by Appenzeller et al. in 2004 [7]. A large number of studies have gradually mapped out a roadmap for the development of TFET, including material design and device structure development, as well as figures of merit for sub-Boltzmann-limit performance (Figure 1B-F). Detailed discussion of these aspects will be developed in the following sections. In short, material innovations including

heterostructure engineering for broken-gap alignments, nanowire development for employing quantum confinement effects in ultrathin-body devices, novel 2D-material integration for interfacial, electrostatic, and band-alignment perfections, and so on were conducted in recent years to optimize the BTBT probability; at the same time, structure development, such as gate-all-around (GAA) structures for enhanced electrostatic control, negative-capacitance TFETs (NC-TFETs, using ferroelectric instead of conventional dielectric layers), and strain superlattices for efficient tunneling-barrier controls, was also promoted in pursuit of high-performance TFETs [8-13].

Early TFET research focused on three-dimensional (3D) bulk materials, such as Si, Ge, and III-V semiconductors, leveraging heterojunctions (e.g., InAs/GaSb, Ge/SiGe) to optimize tunneling efficiency. While these designs demonstrated improved SS values, they still faced critical limitations. For Si or Ge, their large effective carrier mass ( $m^*$ ) and indirect bandgap reduce BTBT probability in related tunnel junctions, resulting in  $I_{ON}$  values orders of magnitude lower than the conventional MOSFETs. Several research have found that interface or lattice engineering may solve this problem to some extent [14, 15]; however, more research turned to develop III-V semiconductors, mainly based on the InAs family, with ultra-small  $m^*$  and ultra-narrow bandgap [16]. In this system, high tunneling probability can be easily demonstrated in theoretical physics model, but the practical experiment has suffered many obstacles. Firstly, InAs needs to be developed into heterojunctions because of its intrinsic narrow bandgap, but this brings problems of lattice mismatch at hetero-interface that introduces traps and degrading SS and current switching ratios. Secondly, nanoscale 3D material channels require additional techniques to improve gate control, such as thinning body-thickness and introducing GAA structures, but it may inadvertently increase bandgaps because of the quantum confinement effects, counteracting tunneling efficiency. These bottlenecks highlighted the need for innovative materials and structures beyond conventional 3D semiconductors.

The discovery of two-dimensional (2D) materials, such as graphene, transition metal dichalcogenides (TMDs), black phosphorus (BP), and indium selenide (InSe), has revolutionized TFET design. Their atomic thickness, pristine surfaces, and layer-dependent electronic properties offer unprecedented advantages [17, 18]. Firstly, 2D material enables superior electrostatic control. The quantum confinement inherent to atomically thin 2D semiconductors ensures that charge carriers are restricted to an ultrathin region, enabling uniform electrostatic modulation via the gate bias. These materials also exhibit inherently short screening ( $\lambda$ ), a critical property for narrowing tunneling barriers and enhancing BTBT efficiency, which provides a direct consequence of steep subthreshold swing physics. Unlike conventional 3D systems (e.g., InAs heterostructures), the van der Waals (vdW) bonding between layers in 2D semiconductors eliminates interfacial dangling bonds and traps, preserving pristine heterojunction quality. Additionally, the layer-dependent bandgap tunability of these materials provides unparalleled flexibility in heterostructure band alignment engineering. Furthermore, the atomically precise thickness of 2D channels suppresses variations in layer uniformity, ensuring abrupt band edge transitions that sharpen the BTBT onset characteristics. Designing and fabricating 2D-material-based tunnel junctions seems to be an ideal solution for TFET development.

**FIGURE 1** | A comparative analysis on the research value and attractiveness of TFET. (A) Vote results from the survey of Emerging Logic Devices in 2014 ERD Emerging Logic Workshop [2]. (B) Quantity of the publications, including research articles, reviews, and patents, regarding TFETs and other attractive beyond-CMOS transistors. KEY WORDS: “tunneling FET,” “carbon nanotube FET,” “nanowire FET -tunneling -carbon,” “nano electro-mechanical switch,” “spin torque transistor,” “SOI lateral bipolar,” “piezotronic transistor,” “2D channel FET -tunneling,” “negative capacitance FET -tunneling,” “ion-implanted transistor.” SEARCH ENGINE: Google Scholar. (C) Quantity proportion of specific papers, including research articles, reviews, and ESI highly cited papers, regarding TFETs and other attractive beyond-CMOS transistors. KEY WORDS: “tunneling transistor,” “negative capacitance transistor,” “carbon nanotube transistor,” “spin transistor,” “nano-electro-mechanical,” “Mott transistor,” “bilayer pseudospin,” “ion implant transistor”. The sum of search results for the last four keywords was used to analyze the term “others.” SEARCH ENGINE: Web of Science. (D) Quantity proportion of publications, as well as (E) ESI highly cited papers, regarding beyond-CMOS transistors and all kinds of transistors. The KEY WORDS used for searching are the same as those in figure (C), but with the addition of “transistor” corresponding to all of its species. SEARCH ENGINE: Web of Science. (F) Annual statistics on the quantity proportion of publications regarding TFETs and two other most-attractive beyond-CMOS transistors. KEY WORDS: “tunneling transistor,” “negative capacitance transistor,” “carbon nanotube transistor.” SEARCH ENGINE: Web of Science.

However, challenges still persist: (1) Controllable and large-scale growth of defect-free 2D layers and heterostructures remains elusive; (2) Contact resistance engineering at metal-2D interface is still a critical problem for every 2D-material-based device; (3) Last but most importantly, since 2D materials are not suitable for precise doping, finding reasonable heterostructures through material design and energy band engineering is the most critical step to achieve high-performance TFET based on 2D materials.

Although several published reviews have summarized the performance advantages of TFET and its development based on various material-systems, there is still a lack of systematic analysis and summary regarding the material design, device construction and architecture innovation of TFET that emphasizes the fundamental field of device physics. Therefore, we hope to provide a review to systematically analyze the evolution of advanced TFETs based on the subthreshold swing device physics, with a focus on design strategies, experimental milestones, and unresolved challenges. After the Introduction, we will devote a section to the device physics of TFET and the

figures of merit in electrical performance, which is a key understanding for the design and development of TFET. Then, there will be two sections discussing the advanced research of high-performance TFET, focusing respectively on the traditional 3D-nanowire TFETs and the emerging 2D-material TFETs. At the end, there is a summary and outlook section, and the practical applications of TFET are further discussed. By bridging material innovation with device physics, we aim to provide a constructive development framework for realizing high-performance TFETs in the post-Moore era.

## 2 | Understanding and Design of High-Performance TFETs

### 2.1 | Subthreshold Swing Physics in MOSFETs

The fundamental performance constraints of conventional FETs originate from the inherent physics governing carrier injection mechanisms. In MOSFETs, the subthreshold current

transport is dominated by thermionic emission, where charge carriers (electrons or holes) must acquire sufficient thermal energy to surmount the energy barrier modulated by the gate voltage ( $V_g$ ). This process adheres strictly to the Boltzmann statistics of carrier distribution, resulting in an exponential dependence of drain current ( $I_{DS}$ ) on  $V_g$  in the subthreshold regime [19]:

$$I_{DS} \propto e^{\frac{qV_g}{nk_B T}}, \quad (1)$$

where  $q$  is the elementary charge,  $k_B$  is the Boltzmann constant,  $T$  is the absolute temperature, and  $n$  (ideality factor) represents the capacitive coupling efficiency between the gate and channel, defined as  $n = 1 + C_{ox}C_d$ . Here,  $C_{ox}$  is the gate oxide capacitance, and  $C_d$  accounts for depletion and interface trap capacitance. The SS, defined as the  $V_g$  required to increase the drain current by one decade, is derived from this exponential relationship [19]:

$$SS = \frac{dV_g}{d(\log I_{DS})} = \ln(10) \frac{nk_B T}{q}. \quad (2)$$

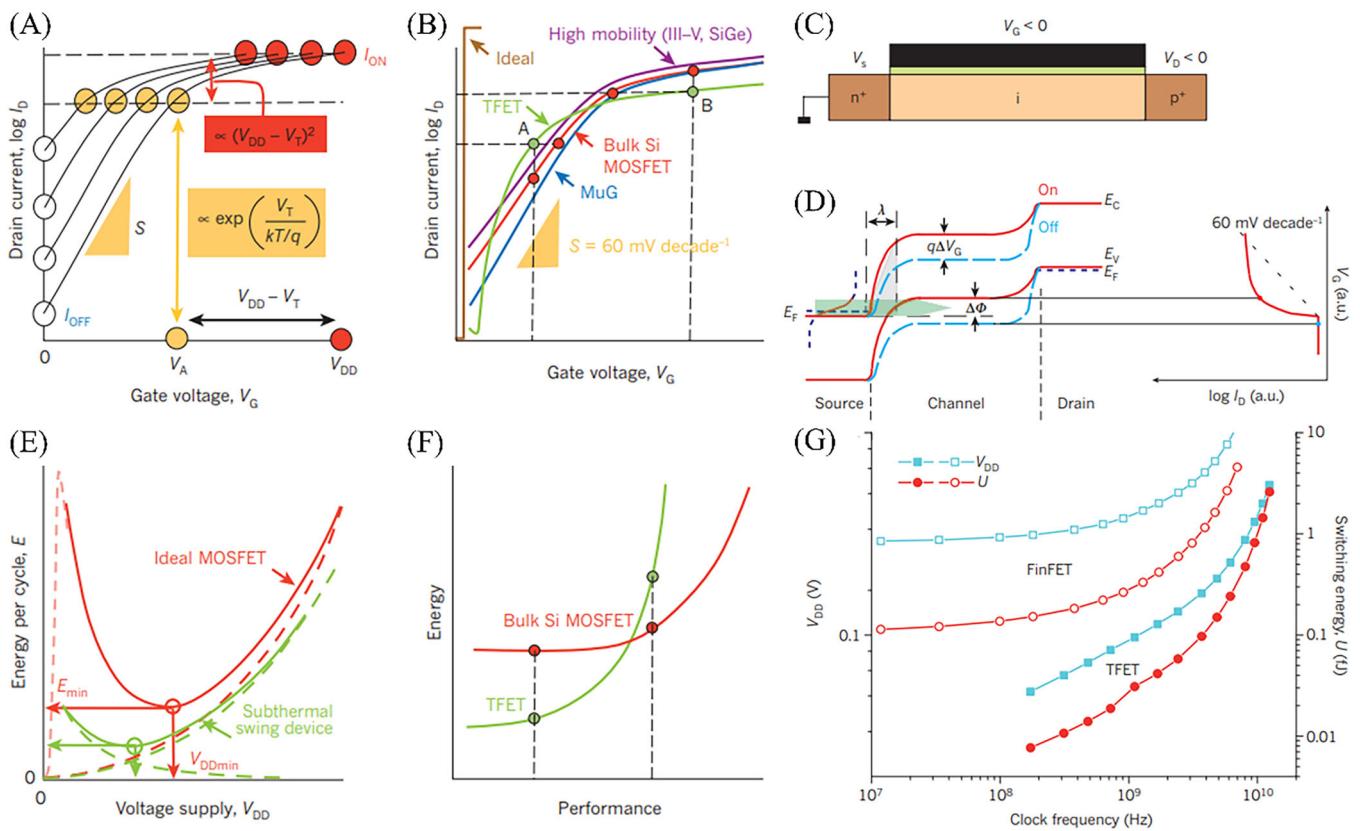

The theoretical minimum SS of  $60 \text{ mV dec}^{-1}$  (when  $n = 1$ ) represents a thermodynamic limit imposed by the Fermi-Dirac distribution of carriers, a phenomenon often termed “Boltzmann tyranny.” This constraint arises because the probability of carriers overcoming the channel barrier decreases exponentially with the barrier height, leading to an inherent trade-off between switching speed (steep SS) and leakage current (Figure 2A) [9].

Recently, the most advanced transistors are close to perfectly implementing  $SS = 60 \text{ mV dec}^{-1}$ . While advanced transistor designs such as FinFETs and FD-SOI devices have improved electrostatic control by reducing SCEs and minimizing  $C_d$ , they remain fundamentally constrained by the Boltzmann limit [20]. For instance, FinFETs leverage 3D gate wrapping to enhance  $C_{ox}$ , thereby lowering  $n$  to near-ideal values ( $\sim 1.0$ ). Similarly, FD-SOI architectures employ ultra-thin body channels to suppress parasitic capacitance. However, as CMOS technology approaches the sub-5 nm regime, the Boltzmann limit becomes a critical bottleneck for power efficiency. Specifically, lowering  $V_{DD}$  below 0.5 V, which is a practical requirement that has been largely touched upon, severely compromises the  $I_{ON}$  and transistor drive capability, necessitating unrealistically steep SS values ( $< 60 \text{ mV dec}^{-1}$ ) to preserve performance, that is, a feat unattainable with conventional thermionic switches. This mandates structural innovations in transistor design to circumvent the Boltzmann limit for future low-power electronics. While advanced architectures mitigate practical non-idealities, they cannot overcome the intrinsic  $60 \text{ mV dec}^{-1}$  SS limit, necessitating exploration of beyond-CMOS technologies for continued progress in semiconductor scaling (Figure 2B) [9].

## 2.2 | Subthreshold Swing Physics in TFETs

TFETs represent a paradigm shift in carrier injection physics by exploiting quantum mechanical BTBT to circumvent the Boltzmann limit inherent in conventional FETs. Unlike thermionic

emission, where carriers require thermal energy to surmount a potential barrier, BTBT enables direct tunneling of carriers between energy bands under the influence of a strong electric field [21, 22]. This mechanism fundamentally decouples carrier statistics from the Boltzmann distribution, enabling SS values below  $60 \text{ mV dec}^{-1}$  at room temperature (Figure 2C,D).

Take a prototypical p-type TFET as an example, a p-i-n heterostructure is employed, where the source is heavily n-doped, the channel is intrinsic (or lightly doped), and the drain is heavily p-doped. Under reverse bias, the energy bands in the source and channel regions align to create a tunneling junction. The  $V_g$  modulates the channel potential, thereby controlling the tunneling window, that is, the energy overlap between the source valence band and the channel conduction band. The tunneling probability is governed by the WKB approximation [23, 24]:

$$T_{WKB} \approx \exp\left(-\frac{4\lambda \cdot \sqrt{2m_T^* \cdot E_g^{\frac{3}{2}}}}{3q\hbar F}\right), \quad (3)$$

where  $\lambda$  is the effective screening length,  $m_T^*$  is the effective carrier mass,  $E_g$  is the material bandgap,  $\hbar$  is the reduced Planck's constant,  $F$  is the electric field across the tunneling junction. Specifically,  $F = E_g + \Delta\varphi$ , and  $\Delta\varphi$  is the energy gap between the source valence-band-maxima (VBM) and the channel conduction-band-minima (CBM), that is, the BTBT energy window. Crucially, the BTBT process exhibits an exponential dependence on  $F$  and  $E_g$ , but only a weak temperature dependence, bypassing the thermal injection constraints of conventional FETs.

The subthreshold behavior of TFET is fundamentally governed by the BTBT mechanism, which displays a hyper exponential  $V_g$  dependence of tunneling probability as described by Equation (3). This characteristic arises from the energy band alignment optimization at the tunnel junction, where a bandgap configuration exceeding the valence band maximum decouples electron population in the source valence band from thermal Fermi-Dirac distribution tail. These phenomena collectively enable TFETs to surpass the Boltzmann limit, achieving sub-60  $\text{mV dec}^{-1}$  SS through quantum mechanical carrier injection rather than thermionic emission. Nevertheless, a comprehensive SS analysis becomes imperative to establish design parameters for TFETs exhibiting sub-thermal swing characteristics of  $< 60 \text{ mV dec}^{-1}$ . To systematically analyze SS and establish design guidelines for sub-thermal TFETs, five critical approximations form the theoretical framework for nanoscale device modeling [25, 26]:

1. Structural Configuration: the prevalent double-gated n-channel architecture with intrinsic channel doping optimizes electrostatic control while minimizing interface-trap density  $D_{it}$ , a configuration validated in advanced FinFET and nanosheet TFET designs.

2. Transport Physics: current conduction follows Landauer's formalism under ballistic/quasi-ballistic conditions, essential for accurately modeling carrier injection in sub-100 nm channel devices where scattering events become negligible.

**FIGURE 2** | TFET as a promising alternative to CMOS transistors: principle and characteristics. Reproduced with permission [9]. Copyright 2011, Springer Nature. (A) Transfer behavior of a MOSFET under voltage scaling reveals exponential  $I_{OFF}$  escalation due to fundamental SS limitations. Proportional reduction of  $V_{DD}$  and threshold voltage  $V_T$  preserves operational current ( $I_{ON}$ ) through maintained overdrive potential ( $V_{DD} - V_T$ ). (B) Comparative analysis of three MOSFET enhancement strategies: multi-gate architectures (blue) enhancing electrostatic control; high-carrier-mobility channels (purple) improving output level; and tunnel FETs (green) demonstrating abrupt switching transitions with minimized leakage currents. (C) Cross-sectional illustration of a p-TFET highlighting voltage-biased source ( $V_S$ ), gate ( $V_G$ ), and drain ( $V_D$ ) terminals. (D) Energy band alignment diagrams contrasting OFF-state (dashed) and ON-state (solid) configurations in p-TFET operation. BTBT initiates when the gate-modulated energy window  $\Delta\varphi$  (shaded region in green) enables charge injection across the barrier. Unlike conventional MOSFETs, TFET current characteristics exhibit nonlinear logarithmic dependence due to quantum tunneling probability and Fermi-level density-of-states constraints. The tunneling mechanism approximates to a triangular barrier model (gray overlay). (E) Minimum switching energy ( $E_{min}$ ) versus optimized supply voltage ( $V_{DDmin}$ ) comparison between theoretical TFET and MOSFET at equivalent  $I_{ON}/I_{OFF}$  current ratios. (F) Energy-performance comparative-analysis demonstrating TFET's superior efficiency at moderate throughput requirements versus MOSFET dominance in high-performance regimes. (G) System-level simulation of scaled InAlAs/GaAlSb TFET (solid markers) versus 20-nm FinFET (open markers) under power-constrained multi-core architecture (24 M transistors). Voltage-frequency co-optimization reveals TFET advantages through adaptive parameter tuning of  $V_{DD}$ ,  $V_T$ , source Fermi level ( $V_e$ ), and dimensional scaling while maximizing clock frequency under thermal budgets.

3. Tunneling Probability Homogeneity: the WKB tunneling probability remains approximately constant within narrow energy windows ( $\Delta\varphi \approx \text{few } kT$ ), valid for subthreshold operation where gate modulation primarily affects band alignment rather than tunneling path geometry.

4. Source-Drain Asymmetry: the Fermi-Dirac distribution contribution becomes insignificant in the tunneling window due to substantial drain-source potential differences ( $>0.1$  V), enabling simplified current modeling focused on source-side injection characteristics.

5. Electrostatic Length Quantification: minimum tunneling length derivation employs one-dimensional (1D) Poisson solutions under Yan's parabolic potential approximation combined with Kane's two-band model, a methodology successfully applied in heterojunction TFET optimization.

When employing a fixed  $V_g$ , that is, a controlled  $\Delta\varphi$ , the tunnelling probability can be expressed based on Yan's parabolic approximation in FET compact modelling:

$$T_{\Delta\varphi} \approx \exp \left( -\pi \cdot \sqrt{2E_g m_T^*} \cdot W_{\text{Tunn}} / 4q\hbar \right), \quad (4)$$

where  $W_{\text{Tunn}}$  is the minimum tunnelling width crossing the junction. Further, according to the Landauer's formalism, the tunnelling current density within the junction region can be defined as:

$$I_T = \frac{2q}{h} \cdot T_{\Delta\varphi} \cdot F_{\text{Integral}}, \quad (5)$$

where  $F_{\text{Integral}}$  is the integral of the Fermi-Dirac distribution function of carriers:

$$F_{\text{Integral}} = k_B T \cdot \ln \left( \frac{1 + \exp \left[ \frac{(E_{F,s} - E_{V,s} + \Delta\varphi)}{k_B T} \right]}{1 + \exp \left[ \frac{(E_{F,s} - E_{V,s})}{k_B T} \right]} \right). \quad (6)$$

Here,  $E_{F,s}$ ,  $E_{V,s}$ , are the Fermi level and VBM in source end, respectively. These approximations collectively define the SS through the relationship through a dual-component model expressed as:

$$SS = \left( \frac{d(\Delta\varphi/q)}{d \log_{10} I_T} \right) = [(SS_T)^{-1} + (SS_{FD})^{-1}]^{-1}, \quad (7)$$

where  $SS_T$  reflects  $V_g$ -induced band alignment modulation:

$$SS_T = \left( \frac{d(\Delta\varphi/q)}{d \log_{10} T_{\Delta\varphi}} \right) = \frac{(2\sqrt{2} \ln 10) \cdot \hbar}{-q\pi \cdot \sqrt{E_g m_T^*}} \cdot \frac{d\Delta\varphi}{dW_{\text{Tunn}}}, \quad (8)$$

and  $SS_{FD}$  arises from the energy separation between the  $E_{V,s}$  and  $E_{F,s}$ :

$$SS_{FD} = \left( \frac{d(\Delta\varphi/q)}{d \log_{10} F_{\text{Integral}}} \right) = \frac{k_B T \cdot \ln 10}{q} \cdot (1 + \exp[(E_{V,s} - E_{F,s} - \Delta\varphi)/k_B T]) \cdot \ln \left( \frac{1 + \exp[(E_{V,s} - E_{F,s} + \Delta\varphi)/k_B T]}{1 + \exp[(E_{F,s} - E_{V,s})/k_B T]} \right). \quad (9)$$

The analytical framework established by Equations (3–9) provides a comprehensive methodology for evaluating SS in TFETs across both nanoscale bulk semiconductor and 2D material implementations [23]. At the tunneling initiation threshold ( $\Delta\varphi \approx 0$ ), the  $[SS]_{FD}$  component theoretically approaches near-zero values due to minimized Fermi-Dirac distribution broadening. However, practical device operation in this regime becomes fundamentally limited by extraneous conduction mechanisms, including reverse-bias junction leakage and trap-assisted tunneling (TAT) currents arising from interface defects [27]. Consequently, the effective SS minimum manifests at finite tunneling energy windows ( $\Delta\varphi \approx kT$ ), where  $SS_T$  dominates through its dependence on gate-modulated band alignment.

The pursuit of optimal TFET performance has centered on reconciling two conflicting objectives: maximizing  $I_{\text{ON}}$  while minimizing SS across multiple decades of subthreshold operation [28]. The enhancement of  $I_{\text{ON}}$  in TFETs necessitates maximization of BTBT probability under minimal gate voltages, a requirement fundamentally governed by three parameters: effective tunneling mass  $m_T^*$ , energy bandgap  $E_g$ , and electrostatic screening length  $\lambda$ . A smaller  $\lambda$  represents superior gate control over tunneling junction electrostatics. Minimizing  $\lambda$ , that is, achieved through gate dielectric thickness scaling ( $<2$  nm) or high- $\kappa$  material integration ( $\text{HfO}_2$ ,  $\text{Al}_2\text{O}_3$ ), strengthens gate field penetration at the tunneling junction, enabling precise electrostatic control. Concurrent elevation of source doping concentration  $N_A$  induces degenerate band bending, further compressing  $\lambda$  through enhanced carrier confinement.  $m_T^*$  is determined by the geometric meaning of

valence ( $m_V^*$ ) and conduction ( $m_C^*$ ) band effective masses, which can benefit from heterostructure engineering. In contrast,  $E_g$  optimization requires strategic source material selection, with narrow-bandgap semiconductors (Ge, InSb) reducing tunneling barrier heights while introducing challenges in off-state leakage management.

The inherent trade-off between SS minimization and  $I_{\text{ON}}$  enhancement in TFETs arises from competing physical dependencies in device operation as shown in Equations (3–9). For instance, while reduced  $E_g$  and  $m_T^*$  improve tunneling probability ( $T_{\text{WKB}}$ ) to elevate  $I_{\text{ON}}$ , these modifications simultaneously amplify the gate sensitivity of band alignment modulation ( $[SS]_T$ ), thereby degrading SS. Similarly, strategies to enhance electrostatic control through increased  $N_A$  and reduced  $\lambda$  shorten tunneling distance ( $W_{\text{Tunn}}$ ) to boost  $T_{\text{WKB}}$  yet induce excessive band bending that strengthens electrostatic screening. This screening effect restricts the  $\Delta\varphi$ -dependent tunability of  $W_{\text{Tunn}}$ , ultimately compromising SS through diminished  $\partial\Delta\varphi/\partial V_g$  response.

The intricate interdependence between electrostatic and material parameters in governing  $I_{\text{ON}}$  and SS necessitates balanced optimization strategies for TFETs. Achieving this equilibrium requires systematic co-engineering of device architecture and material properties, particularly focusing on three critical aspects: doping gradient precision at tunneling junctions, optimized gate dielectric configurations, and strategic selection of semiconductor materials with tailored electronic characteristics. While reduced carrier effective mass and narrow bandgap materials demonstrate potential for enhancing tunneling probability, their excessive minimization introduces detrimental tradeoffs.

Also, the ultra-low effective masses paradoxically diminish the density of available quantum states in both conduction and valence bands, potentially degrading the  $I_{\text{ON}}/I_{\text{OFF}}$  ratio through constrained tunneling pathways. Concurrently, extreme bandgap narrowing in source regions promotes significant BTBT leakage currents, exacerbating  $I_{\text{OFF}}$  degradation and consequently compromising subthreshold operational integrity. These phenomena collectively underscore the nontrivial nature of TFET performance optimization, where quantum mechanical transport mechanisms impose strict boundaries on material parameter selection. The design paradigm therefore emphasizes synergistic adjustments across multiple device domains rather than unilateral parameter optimization, requiring meticulous consideration of interdependencies between quantum confinement effects, band structure engineering, and electrostatic control methodologies.

### 2.3 | Figures of Merit in TFET Performance

The viability of high-performance TFETs hinges on optimizing four critical metrics:

1. SS Features: governs switching abruptness. Critical requirements include a minimum SS ( $SS_{\text{min}} \leq 40 \text{ mV dec}^{-1}$ ), as well as an average SS ( $SS_{\text{avg}} \leq 60 \text{ mV dec}^{-1}$ ) across a rational range of subthreshold current span  $> 4$  orders of magnitude

( $I_{\text{sub-ratio}} > 10^4$ ). Superior switching necessitates sustained  $SS_{\text{avg}}$  performance rather than isolated  $SS_{\text{min}}$  improvements, as steep  $SS$  degradation nullifies subthreshold advantages despite low  $SS_{\text{min}}$ .

2. On-State Current ( $I_{\text{ON}}$ ): determines operational speed. A subthreshold figure of merit,  $I_{60}$ , representing the BTBT current at which  $SS$  remains sub-60 mV dec $^{-1}$  (@ 300 K), serves as a standardized metric.  $I_{60}$  exhibits saturation under moderate lateral fields ( $\sim 1 \times 10^5$  V cm $^{-1}$ ) and correlates with  $SS_{\text{avg}}$  stability and high  $I_{\text{ON}}/I_{\text{OFF}}$  ratios. Competitiveness with MOSFETs mandates  $I_{60}$  to be at least within 1–10  $\mu\text{A}/\mu\text{m}$  region (for low-power devices) or even higher (for high-output circuits), normalized to equivalent drain-field conditions ( $V_{\text{DS}}/L_{\text{ch}} = 1 \times 10^5$  V cm $^{-1}$ ) to decouple drain-bias dependencies.

3.  $I_{\text{ON}}/I_{\text{OFF}}$  Ratio: essential for noise immunity. For low-power applications, normally a current-switching ratio over  $10^5$  is required. Unless TFET can raise the  $I_{\text{ON}}$  to the operating range of high-performance CMOS (HP-CMOS, perhaps greater than 10 mA  $\mu\text{m}^{-1}$ ), it is necessary to demonstrate a considerable  $I_{\text{ON}}/I_{\text{OFF}}$  ratio.

4. Dynamic Performance: power-delay product (PDP, estimating the switching energy of transistor) and intrinsic delay ( $\tau$ ) are primarily governed by gate capacitance ( $C_g$ ) and  $I_{\text{ON}}$  [29]:

$$\tau = \frac{C_g V_{\text{DD}}}{I_{\text{ON}}}, \quad (16)$$

$$\text{PDP} = C_g V_{\text{DD}}^2. \quad (17)$$

$V_{\text{DD}}$  downscaling coupled with  $I_{\text{ON}}$  increasing and  $C_g$  lowering enables simultaneous power reduction and speed improvement.  $C_g$  minimization requires synergistic optimization of gate stack design (e.g., dielectric scaling, quantum capacitance modulation), drain doping gradients, and channel (or structural) material selection. Device engineering must therefore address both electrostatic control and quantum transport limitations to advance TFET circuit viability.

**TABLE 1** | Figures of merit of high-performance TFET and the advanced results in various types of tunnel junctions.

| Junction                            | Type                       | $SS_{\text{min}}$<br>(mV dec $^{-1}$ ) | $SS_{\text{avg}}$<br>(mV dec $^{-1}$ ) <sup>a</sup> | $I_{60}$ ( $\mu\text{A}/\mu\text{m}$ ) <sup>b</sup> | $I_{\text{ON}}/I_{\text{OFF}}$ | Ref. |

|-------------------------------------|----------------------------|----------------------------------------|-----------------------------------------------------|-----------------------------------------------------|--------------------------------|------|

| —                                   | Figures of merit           | << 40 Prefer<br>Smaller                | << 60 Prefer<br>Smaller                             | > 1 Prefer<br>Higher                                | > $10^5$ Prefer<br>Lager       | —    |

| Si                                  | 3D nanowire                | 30                                     | 50                                                  | 0.001                                               | $10^4$                         | [30] |

| InAs/GaSb                           | 3D heterojunction          | 50                                     | 59                                                  | ~1                                                  | $10^6$                         | [31] |

| InGaAs/InAs                         | 3D heterojunction          | 55                                     | 60                                                  | 0.008                                               | $> 10^5$                       | [32] |

| Ge/MoS <sub>2</sub>                 | 2D/3D mix-dimensional      | ~5                                     | 30                                                  | 0.001                                               | $10^{10}$                      | [33] |

| Si/InSe                             | 2D/3D mix-dimensional      | ~5                                     | 10                                                  | ~0.1                                                | $10^5$                         | [34] |

| MoTe <sub>2</sub>                   | 2D homojunction            | 30                                     | 50                                                  | —                                                   | $10^7$                         | [35] |

| BP                                  | Bulk-monolayer<br>junction | 20                                     | 30                                                  | ~1                                                  | $10^6$                         | [36] |

| WSe <sub>2</sub> /SnSe <sub>2</sub> | 2D heterojunction          | 20                                     | 60                                                  | —                                                   | $> 10^5$                       | [37] |

<sup>a</sup>Calculated within the switching current range of more than three orders of magnitude.

<sup>b</sup>Normalized @  $V_{\text{DD}} = 1$  V.

These criteria underscore the necessity for material-to-device interdisciplinary optimization to balance steep switching, current drive, leakage suppression, and dynamic efficiency in TFET designs. In Table 1, we summarize these important performance indicators and list the advanced results in various types of reported TFETs [30–37]. It should be noted that in the existing TFET studies, PDP and  $\tau$  have not been widely valued; in the vast majority of reports, quantitative tests on these two indicators have not been conducted yet. Hence, we have not included these two indicators for the time being in Table 1.

## 2.4 | Benchmarking of TFET and Other Transistors

TFETs exhibit several advantages over traditional CMOS transistors. One of the most notable benefits is their ability to operate at significantly lower supply voltages. Unlike CMOS, which requires higher voltages to ensure sufficient turn-off of the transistor and suppress standby power dissipation, TFETs utilize BTBT to achieve efficient switching at low voltages, as summarized in Table 2 and Figure 2E–G [4, 9]. Additionally, TFETs exhibit a smaller gate capacitance due to gate-drain underlaps, contributing to faster switching times and lower power consumption. The negative differential resistance (NDR) characteristic of TFETs also provides unique advantages in designing low-power logic circuits, allowing for more flexible and efficient circuit designs.

In terms of circuit area, TFETs demonstrate competitive performance with CMOS. The area of a TFET inverter with a fan out of 4 is calculated to be comparable to that of a CMOS inverter, despite the additional complexity of the TFET structure. This is attributed to the smaller gate capacitance and the efficient use of space in TFET designs. For more complex circuits like 32-bit adders, the area overhead of TFETs remains manageable, making them suitable for integration into larger systems. The energy-delay product (EDP), a key metric for evaluating the efficiency of logic devices, is found to be significantly lower for TFETs compared to CMOS. This is primarily

**TABLE 2** | Benchmarking on 32-b adders based on TFETs and conventional MOSFETs.

| Parameter                   | TFETs        | High-performance CMOS | Low-power CMOS |

|-----------------------------|--------------|-----------------------|----------------|

| Supply Voltage ( $V_{DD}$ ) | 0.2–0.4 V    | 0.73 V                | 0.3 V          |

| Drive Current ( $I_{ON}$ )  | 25–500 A/m   | 1805 A/m              | 2 A/m          |

| Switching Energy            | 0.15–0.59 fJ | 2.48 fJ               | 0.42 fJ        |

| Switching Delay             | 138–1378 ps  | 84 ps                 | 31,331 ps      |

**TABLE 3** | Benchmarking on TFETs and other beyond-CMOS devices.

| Device                           | Supply voltage (V) | 32-bit Adder area ( $F^2$ ) | Intrinsic delay (ps) | Switching energy (aJ) | Power density (W/cm <sup>2</sup> ) | Throughput (PIOPS/cm <sup>2</sup> ) |

|----------------------------------|--------------------|-----------------------------|----------------------|-----------------------|------------------------------------|-------------------------------------|

| <b>TFET Family</b>               |                    |                             |                      |                       |                                    |                                     |

| HomJTFET                         | 0.2                | 373,250                     | 3.27                 | 0.98                  | 0.1                                | 0.86                                |

| HetJTFET                         | 0.4                | 373,250                     | 0.33                 | 3.93                  | 5.1                                | 8.64                                |

| gnrTFET                          | 0.25               | 373,250                     | 0.79                 | 1.53                  | 0.8                                | 3.60                                |

| <b>Other Beyond-CMOS Devices</b> |                    |                             |                      |                       |                                    |                                     |

| GpnJ                             | 0.7                | 207,360                     | 2.17                 | 142.77                | 301.5                              | 19.47                               |

| BisFET                           | 0.6                | 454,900                     | 1.36                 | 22.10                 | 5.8                                | 1.92                                |

| SpinFET                          | 0.7                | 279,940                     | 1.02                 | 30.08                 | 18.0                               | 5.63                                |

| STT/DW                           | 0.01               | 30,240                      | 1762.9               | 111.06                | 6.5                                | 0.13                                |

| SMG                              | 0.01/0.1           | 13,824                      | 297.61               | 1.38                  | 0.3                                | 0.84                                |

| STTtriad                         | 0.01               | 165,240                     | 298.03               | 10.92                 | 0.3                                | 0.02                                |

| STOlogic                         | 0.01               | 27,648                      | 1000                 | 351.60                | 23.5                               | 0.23                                |

| SWD                              | 0.01/0.1           | 9216                        | 297.61               | 1.38                  | 1.1                                | 3.99                                |

| NML                              | 0.01/0.1           | 4608                        | 400                  | 19.31                 | 3.1                                | 2.51                                |

| ASLD                             | 0.01               | 9216                        | 205.16               | 108.20                | 38.2                               | 1.84                                |

due to the reduced switching energy and faster switching times of TFETs at low supply voltages. For example, a 32-bit adder implemented with TFETs can achieve an EDP of approximately 20.7 fJ·ps, which is at least an order of magnitude lower than that of CMOS-based adders under similar operating conditions.

Moreover, TFET demonstrates distinct advantages and trade-offs when quantitatively compared to alternative beyond-CMOS logic devices, as evidenced by standardized metrics stated in Table 3 [4]. Homojunction TFETs (HomJTFET) and graphene-nanotube TFETs (gnrTFET) achieve the lowest switching energy among all evaluated devices at 0.2 V, outperforming graphene pn-junction (GpnJ) devices and approaching the energy efficiency of voltage-controlled spintronic devices like spin wave devices (SWD). However, TFETs suffer from area penalties due to doping isolation requirements, with 32-bit adder areas ( $373,250 F^2$ ) nearly 1.8× larger than GpnJ and 12× larger than nanomagnetic logic (NML). Heterojunction TFETs (HetJTFET) address speed limitations of HomJTFET, reducing intrinsic delay from 3.27 ps to 0.33 ps at 0.4 V, rivaling CMOS HP (0.25 ps) but at the cost of higher energy (3.93 aJ vs. CMOS HP: 19.63 aJ).

Spintronic devices exhibit divergent performance profiles. While spintronic majority gate (SMG) and spin torque triads (STTtriad)

achieve ultra-low energy, its delay renders it impractical for high-speed applications compared to HetJTFET. Spin-transfer torque domain wall (STT/DW), spin torque oscillator (STO) logic, and all-spin logic (ASLD) show moderate energy but suffer from latency exceedingly even HomJTFET's circuit-level delay. NML and SWD leverage voltage-controlled operation to minimize energy, yet their delays remain orders of magnitude higher than TFET variants. On the other hand, bilayer pseudospin FETs (BisFETs), though theoretically promising with 1.36 ps delay and 22.10 aJ energy, face unresolved scalability challenges, as their 32-bit adder area exceeds TFETs by 22%. Also, spinFETs, hybrid CMOS-magnetic devices, mimic conventional transistor speeds but incur higher energy than HetJTFET.

In summary, TFETs occupy a unique niche, combining near-CMOS speeds with ultralow energy consumption, albeit constrained by area inefficiencies. TFETs offer compelling advantages for low-power and low-voltage applications, with significant improvements in switching energy, delay, and EDP compared to traditional CMOS transistors. While spintronic alternatives excel in nonvolatility or functional density, their reliance on slow magnetization dynamics and peripheral circuitry limits competitiveness in conventional logic. Experimental validation of TFET heterostructures and doping techniques remains critical to closing

the performance gap with CMOS while retaining energy advantages. However, their adoption is tempered by manufacturing complexities and performance limitations in high-speed contexts. As research continues to advance material science and device physics, TFETs and other beyond-CMOS devices are expected to play increasingly important roles in the evolution of integrated circuits, potentially leading to new paradigms in computing technology. The ongoing optimization of TFETs, alongside the exploration of novel materials and architectures, is anticipated to address current limitations and further enhance their competitiveness in the nanoelectronics landscape.

## 2.5 | Designing High-Performance TFETs Based on Device Physics

The development of TFETs into mainstream semiconductor technology requires a systematic roadmap addressing material innovation, device architecture optimization, and fabrication advancements. Below, we will briefly draw a roadmap for the future development of TFET, and expand on these synergistic strategies, supported by recent breakthroughs and computational insights. A detailed discussion will be carried out in the following chapters. First of all, the most important part of TFET research is the design of efficient tunnel junctions. According to the sub-threshold swing device physics we discussed in the early section, the most critical pass arises in the innovation on junction materials exhibiting ultra-low effective carrier mass ( $m^*$ ), ultra-narrow bandgap, and high mobility. Carriers with low  $m^*$  exhibit higher tunneling probabilities due to reduced tunneling distance. On the other hand, the tunnel junction may be optimized through strain engineering, for example, the uniaxial tensile strain is suggested to reduce  $E_g$  and  $m^*$  simultaneously in some materials. Strain gradients may also suppress ambipolarity by selectively modulating band alignment at source/drain interfaces. In addition, emerging 2D materials may also provide effective assistance for the design of efficient tunneling junctions. Notably, what is referred to here is not the direct use of 2D materials for the construction of tunneling junctions, but the use of interlayer screening effects in vdW stacked 2D materials to achieve unprecedented electrostatic control. In this regard, challenges include interlayer contamination and thermal resistance at heterointerfaces. Initial attempts at van der Waals integration centered on depositing high- $\kappa$  dielectrics onto sensitive channel materials to form interfaces with minimal chemical disorder and trap states, which are crucial for effective electrostatic gating [38]. This methodology extends beyond passive dielectric integration to enable active current-carrying junctions through lithographically patterned metal electrodes transferred onto two-dimensional semiconductors. Such interfaces achieve near-ideal characteristics: atomic cleanliness and Fermi-level pinning suppression allow operation approaching the Schottky-Mott theoretical limit, a benchmark challenging to attain in conventional metallization schemes [39]. These pinning-free van der Waals contacts can be harnessed to create highly efficient photodiodes with minimal interfacial recombination and near-perfect internal quantum efficiency, offering valuable insights into the development and application of emerging TFET devices [40].

In addition to material science, device physics is also an important optimization direction for TFETs. First, also

derived from the understanding of the physical formula of step-slope devices, improving the control ability of the gate electrostatic field is the most critical step. Prominent structural schemes include the GAA structure, as well as multi-gate designs, in which the dual- or triple-gate architectures decouple control of tunneling and transport regions. On the other hand, innovative device theory or structure may further broaden the development path of TFET. Dirac-source (DS) configurations or NC integrations are admirable examples in this direction, but key challenges include minimizing hysteresis and ensuring ferroelectric phase stability under cycling. Further, the fabrication technologies of both materials and devices also play a significant role in demonstrating high-performance TFETs. Due to the limitations of 3D-InAs system in the development of TFET, the most widely concerned research direction has shifted to 2D materials. However, the large-scale preparation and stability of high-quality 2D materials and vdW heterostructures has not yet been effectively solved, and this will be one of the most important technical cornerstones. In addition, precise doping of 2D materials could also be a valuable technique. On the other hand, innovations on device fabrication are also required because the biggest disadvantage of TFETs is that the output current level is insufficient. Selective edge-bonded metal contacts may bypass Schottky barriers in 2D materials, which is conducive to the increase of currents. It should be noted that although TFET based on traditional 3D materials has encountered a relatively obvious development bottleneck, many innovative works are still emerging in an endless stream. On the other hand, although TFET based on novel 2D materials shows great development potential and theoretically ideal properties, practical experimental results have yet to demonstrate convincing performance. Therefore, in the next two sections, we will review the research reports of TFET based on the most advanced 3D nanowires, and TFET based on the emerging 2D materials, respectively, summarizing their development and prospects.

TFETs offer a compelling pathway to overcome the Boltzmann tyranny by leveraging quantum mechanical tunneling. While their sub-60 mV dec<sup>-1</sup> SS and ultra-low  $I_{OFF}$  are transformative for energy-efficient electronics, practical adoption hinges on resolving material and design challenges. The subthreshold physics of TFETs underscores the interplay between quantum tunneling, material interfaces, and band structure engineering. Advances in low-dimensional materials and heterostructure design have enabled SS values approaching 25 mV dec<sup>-1</sup>, yet practical deployment demands solutions to synthesis, variability, and integration challenges. The TFET roadmap highlights a codesign philosophy integrating novel materials, advanced device architecture, and atomic-scale fabrication. While Technology Computer Aided Design (TCAD) projections are promising, bridging the gap to commercialization demands solutions to variability, thermal stability, and integration complexity. Notably, machine learning may drive the design of TFETs: establishing the library of tunnel junctions will be helpful to further explore the optimal design strategy. With sustained innovation, TFETs could redefine energy-efficient computing, enabling sub-0.5 V operation for internet of things (IoT), artificial intelligence (AI), and future beyond-Moore technologies.

### 3 | Heteroepitaxial Nanowire TFETs

The earliest studies of TFET started from the homojunction of Si or Ge, which was controlled by doping to form the tunnel junction. However, despite structural advancements, Si-based TFET implementations exhibit generally compromised performance metrics. For example, an advanced Si-TFET with a 2-nm gate oxide and a 70-nm SOI layer still has an  $I_{ON}/I_{OFF}$  ratio significantly inferior to conventional MOSFETs. Researchers believe that reducing the thickness of the gate oxide and SOI layer, employing smaller bandgap channel materials, and engineering an abrupt source doping gradient are predicted to boost  $I_{ON}/I_{OFF}$ . In particular, steep source doping profiles can increase  $I_{ON}$  by reducing the tunneling barrier width [41]. Experimental implementations using SiGe/Ge sources and steep doping implants have yielded measurable improvements in SS and drive current [42]. However, these approaches still fall below the driving capability required for high-performance circuits. A large number of device physics studies have shown that the tunneling probability in TFETs depends exponentially on the sharpness of the doping profile at the source–channel interface [21, 22, 43]. The abrupt junction (doping gradient  $<3\text{ nm dec}^{-1}$ ) concentrates the electric field ( $F$ ) at the tunnel junction, maximizing the BTBT probability. Due to the transverse dispersion and segregation of dopants, it is difficult for conventional implantation or diffusion based doping techniques to achieve such abruptness. In this regard, heterojunctions can provide the perfect solution [44–46]. Therefore, in this review, we will skip the discussion of graded doping junction and start with the heterojunction systems based on heteroepitaxial nanowire that have become the most mainstream research direction in the past decade. Heteroepitaxial nanowire TFETs leverage atomic-level interface engineering to optimize tunneling efficiency through precise control of lattice matching and band alignment. Recent advancements in material systems and quantum confinement effects have enabled breakthroughs in both performance and scalability.

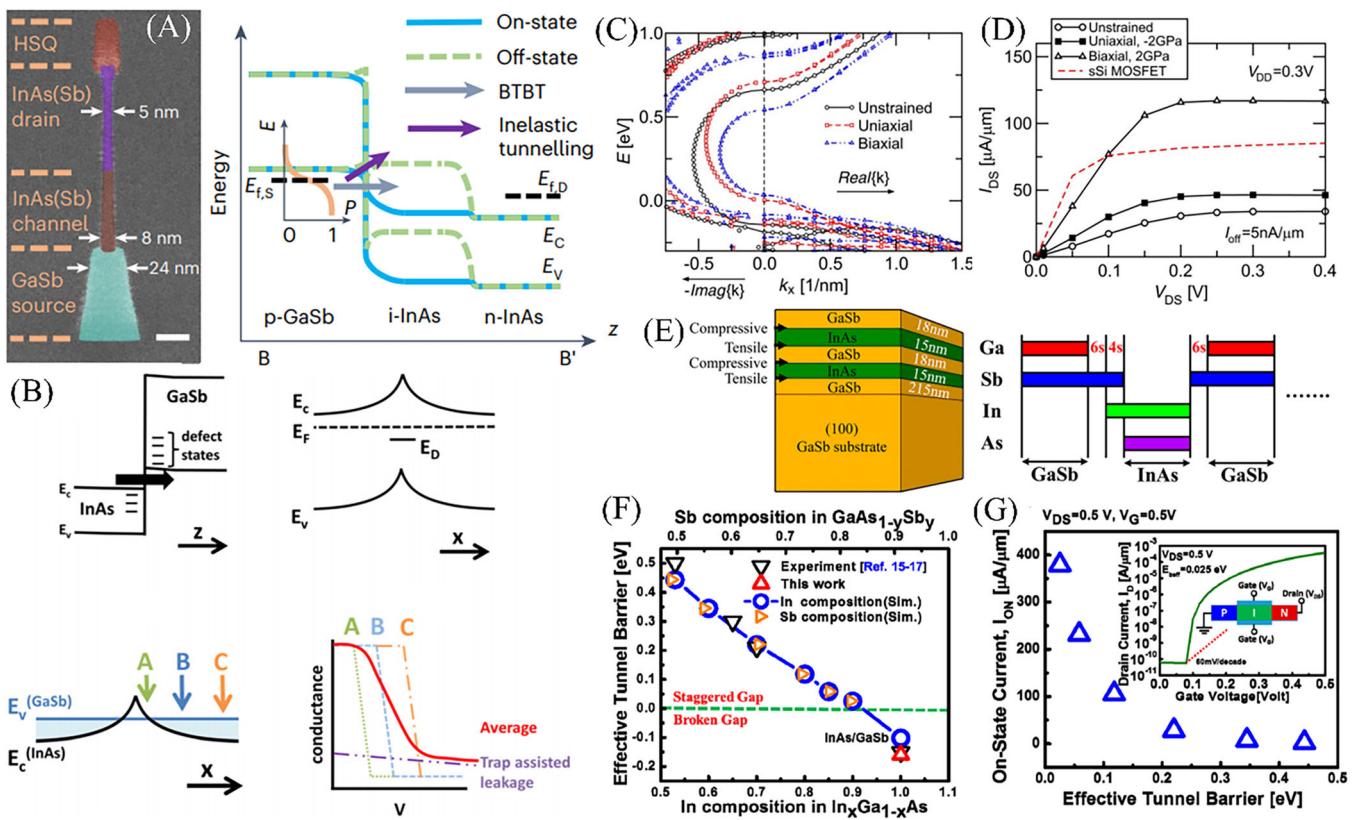

#### 3.1 | Design of Material System: Epitaxial Lattice and Band Structure

InAs was discovered in the study of TFET architecture because it presents the optimal solution so far for the requirements of ultra-small  $m^*$  and ultra-narrow bandgap. At the same time, as a member of group III–V semiconductors, it can be built into high-quality heterostructures with many other lattice-matched semiconductors, such as GaSb, through a mature heteroepitaxy technology system, and show abrupt junctions for carrier tunneling (Figure 3A) [31]. InAs/GaSb nanowires with ultra-small lattice mismatch enables dislocation-free interfaces (small  $D_{lt}$ ) that critical for high tunneling probability. Notably, misfit dislocations still form in InAs on GaSb due to relaxation as a result of large strain from intermixed compositions (Figure 3B) [47]. On the other hand, these nanowire structures can be engaged with further structural and band engineering, such as strain modulation. Figure 3C,D show an example: biaxial stress perpendicular to the transport direction can remarkably improve the  $I_{OFF}$  versus  $I_{ON}$  tradeoff in InAs tunnel FETs and help open an  $I_{OFF}$  and  $V_{DD}$  window where tunnel FETs may outperform Si MOSFETs [48]. This model identifies stress configuration with great potential for

high-performance InAs TFETs. A multi-layer structure with precisely controlled growth based on molecular beam epitaxy (MBE) technology is an experimental example: the output current is increased by orders of magnitude (Figure 3E–G) [49]. In addition to the lattice design of heterostructures, energy band engineering is also an important research topic. Currently, InAs-based heterostructures is the most stable and attractive system to achieve high performance TFET. InAs/GaSb axial superlattices exhibit type-III (broken-gap) alignment that creates a staggered overlap between the source valence band and channel conduction band, eliminating the need for carriers to tunnel through the entire bandgap. Further, multiple heterogeneous layers were designed to pursue more optimized structures with near-zero effective  $E_g$  as well as abrupt junction [46, 50]. In addition, the construction of nanowires is a key step in this system, because the quantum confinement effect shows a significant influence on the energy band regulation of group III–V semiconductors.

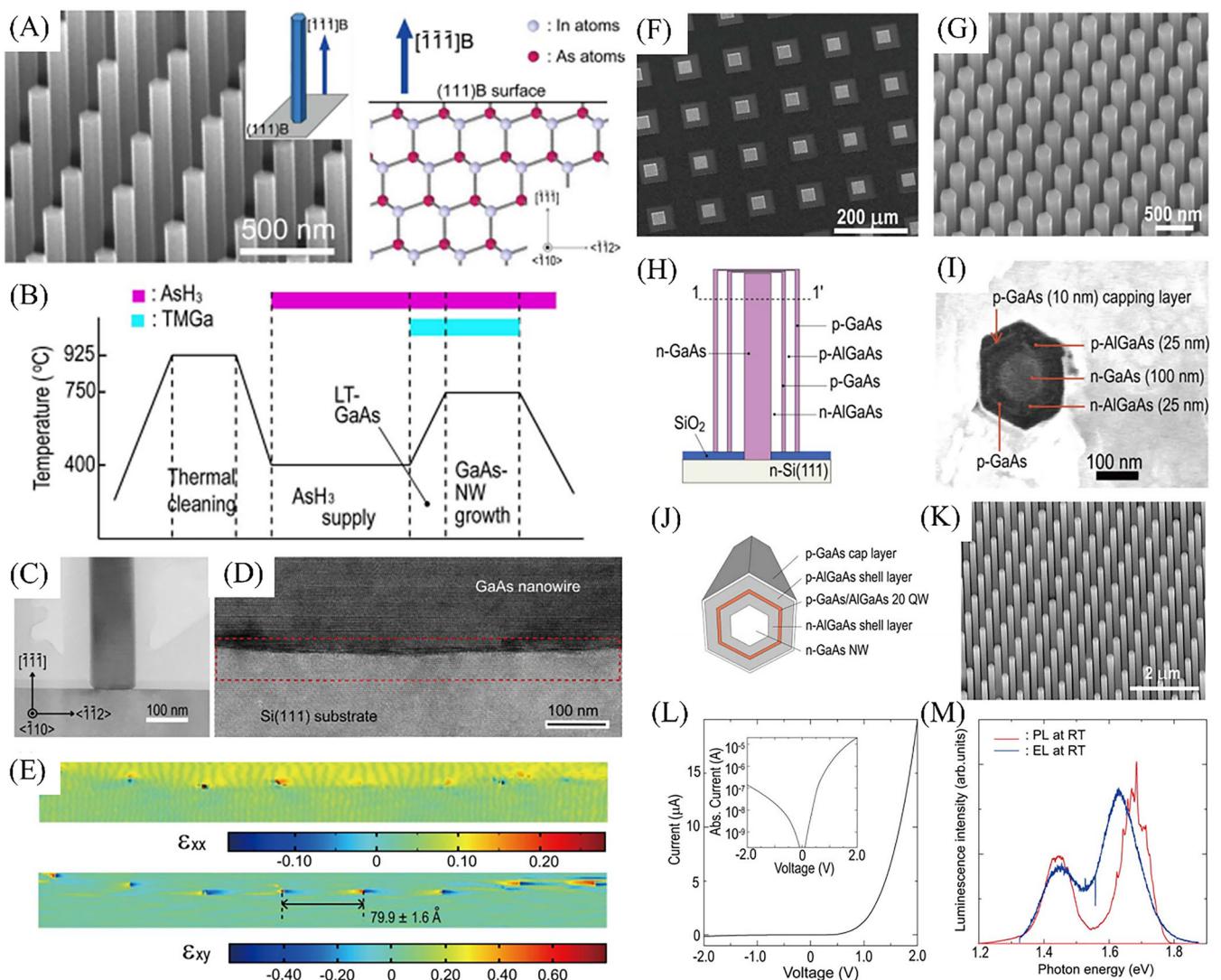

Although the InAs-related heterostructures are currently the most promising system for TFETs, it still faces insurmountable obstacles, especially on experiments. First, as with all 3D heterojunctions, the problem of interfacial defects prevents further performance improvements in InAs-related TFETs [50–52]. In addition, junction gradients at junction interface also degrade  $I_{ON}$  and SS [32, 53, 54]. Although this problem has been blamed more in earlier Si- or Ge-based tunnel junctions, it also needs further optimization in InAs-based TFETs. In this regard, the main means of optimization is to effectively control the nanowire growth stage. Technologies such as MBE and selected area epitaxy (SAE) are effective solutions (Figure 4) [55–57]. This technique leverages precursor flux modulation to suppress defect formation. The result shows that optimization on the tunnel-junction abruptness and pursue of defect-less interface is meaningful. Secondly, group III–V semiconductors generally show narrow bandgaps, which makes the designed TFET unable to effectively suppress  $I_{OFF}$ , and the application prospect of related devices is compressed from the side. In addition, the research progress of large-scale preparation strategy is also very important. Breakthrough has been made in the wafer-scale growth of III–V nanowire arrays through SAE with  $<5\%$  diameter variation, but further application in the preparation and development of large-scale tunnel-junction arrays remains to be studied.

#### 3.2 | Electrostatic Gate-Control Performance: A Bottleneck

The electrostatic control of tunneling junctions in nanowire-based TFETs remains a critical challenge, despite advancements in material properties and device architectures. Below, we expand on the key bottlenecks and emerging solutions, supported by experimental and computational insights. First of all, one major problem faced by nanowire transistors is the diameter-dependent screening effect, because the reduced surface-to-volume ratio in ultra-scaled nanowires degrades gate coupling efficiency. For sub-20-nm-diameter nanowires, the gate coupling efficiency significantly drops due to weakened electrostatic field penetration. To address this, researchers developed GAA architecture that enhanced field penetration by surrounding the nanowire with dielectric and gate metals, greatly improving the output

**FIGURE 3** | Lattice engineering in nanowire TFETs. (A) Architecture of an Esaki diode based on a nanowire heterojunction, accompanied by illustrated energy band profiles for a vertical nanowire transistor. Critical parameters include the lowest conduction subband ( $E_c$ ), highest valence subband ( $E_v$ ), and Fermi level of source ( $E_{f,S}$ ) and drain ( $E_{f,D}$ ). Inset: temperature-dependent Fermi–Dirac distribution within the source, with energy ( $E$ ) and occupation probability ( $P$ ) axes labeled. Scale bars: 20 nm. Reproduced with permission [31]. Copyright 2012, Springer Nature. (B) InAs/GaSb heterojunction band alignment, indicating electron tunneling direction (arrow) and interface defect states ( $E_D$ ) contributing to trap-assisted conduction. Three interfacial valence band configurations (A, B, C) correlate with distinct conductance–voltage characteristics. Experimental conductance (in red) demonstrates reduced slope from combined tunneling mechanisms and leakage pathways. Reproduced with permission [47]. Copyright 2014, AIP Publishing LLC. (C) Comparative energy dispersion analysis for InAs nanowires ( $5 \times 5$  nm cross-section) under three mechanical states: unstrained, uniaxial compression (applying  $T_{xx}$ ), and biaxial tension (applying  $T_{yy} = T_{zz}$ ). Potential energy reference set at wire interior. (D) Comparative current–voltage characteristics between InAs tunnel FET and Si MOSFET at equivalent gate overdrive ( $V_{GS} = V_{GS, off} + V_{DD}$ ,  $V_{DD} = 0.3$  V,  $I_{OFF} = 5$  nA  $\mu\text{m}^{-1}$ ). (C, D) Reproduced with permission [48]. Copyright 2012, IEEE. (E) Multilayer InAs/GaSb heterostructure schematic with MBE growth sequence detailing InSb interfacial layers and Sb surface treatments. Stress states at substrate interfaces: tensile at InAs/GaSb, compressive at GaSb/InAs. (F) Experimental versus simulated effective barrier heights ( $E_{eff}$ ) across GaAs<sub>1-y</sub>Sb<sub>y</sub>/In<sub>x</sub>Ga<sub>1-x</sub>As compositional variations, demonstrating theoretical consistency. (G) Simulation results showing  $I_{ON}$  dependence on effective tunneling barrier height. (E–G) Reproduced with permission [49]. Copyright 2015, American Chemical Society.

performance of TFETs [58–62]. On the other hand, the parasitic capacitance ( $C_{gd}$ ) trade-off is also a critical problem because  $C_{gd}$  between gate and drain limits switching speed and energy efficiency [63]. On this regard, high- $\kappa$  (or low- $\kappa$ ) spacers (or dielectric pockets) may provide a good help [64–67]. Moreover, engaging ferroelectrics seems to be another useful option. Pb(Zr, Ti)O<sub>3</sub> or Si-doped HfO<sub>2</sub> dielectric integrated into nanowires induces NC effects, offering dual advantages for TFETs: (i) substantial improvements in device performance, such as ultra-steep switching and expanded steep-slope region attributed to the voltage-amplification effect of NC, and (ii) reduction on  $I_{OFF}$  and effective suppression on ambipolar behavior facilitated by voltage-pinning effect from ferroelectrics [68, 69]. In summary, electrostatic control remains a pivotal challenge for TFET scalability. Innovations in GAA architectures, SAE growth, and high- $\kappa$ /ferroelectric integration offer promising pathways to overcome these limitations [70]. Future breakthroughs in strain engineering

and hybrid material systems could further push the boundaries of sub-60 mV dec<sup>-1</sup> operation, positioning TFETs as a cornerstone of post-Moore electronics.

### 3.3 | Innovations and Prospects

Heteroepitaxial nanowire TFETs represent a frontier in post-Moore electronics, with lattice engineering and band structure tailoring enabling sub-60 mV dec<sup>-1</sup> operation. In recent years, the research enthusiasm about InAs-related TFET has begun to decline, which may be due to the fact that it has been difficult to obtain substantial breakthroughs in device performance under the existing structure. Therefore, in this review, we look forward to several innovative directions of device structure development, hoping to further promote the continued evolution of related TFET. Firstly, it might be a promising direction to develop hybrid

**FIGURE 4** | SAE-processed nanowire for advanced TFET applications. Reproduced with permission [55]. Copyright 2011, IEEE. (A) Scanning electron microscope (SEM) micrograph illustrating InAs nanowire arrays grown epitaxially on InAs(111)B substrates, with structural schematic of the substrate. Cyan arrow indicates nanowire synthesis orientation. (B) Epitaxial growth protocol for GaAs nanowires on Si(111), highlighting low-temperature nucleation phase. (C) Low-resolution transmission electron microscope micrograph depicting GaAs/Si(111) interfacial region with electron beam aligned along  $<-110>$  zone axis. (D) High-magnification transmission electron microscopy (TEM) view corresponding to panel C. (E) Strain field analysis ( $\epsilon_{xx}$  and  $\epsilon_{xy}$  components) derived from geometric phase analysis of red-dashed region in D. (F) Topographic overview of patterned substrate supporting core-multi-shell (CMS) nanowire arrays. (G) Oblique-view ( $30^\circ$  tilt) SEM characterization of CMS nanowire morphology. (H) 3D schematic representation of CMS architecture. (I) Cross-sectional SEM image obtained along H's dashed profile (1–1'). (J) Structural schematic detailing AlGaAs/20-quantum-well/AlGaAs confinement layers in CMS cross-section. (K) Crystallographic analysis of CMS nanowire growth outcomes. (L) Current–voltage characteristics of CMS devices, with inset displaying semi-logarithmic transport behavior. (M) Comparative optoelectronic spectra demonstrating electroluminescence (EL, blue) and photoluminescence (PL, red) emission from CMS nanostructures. Compared with those based on novel 2D materials, TFETs based on nanowire heterostructure possess a relatively mature and stable technology for material preparation and device fabrication.

dimensional designs, that is, to further develop functional layers at the contact periphery of the nanowires, providing functional modulations with specific benefits. For example, combining DS materials with nanowires may leverage both steep switching and high mobility [71, 72]. Secondly, strain-programmable TFETs, realizing through piezoelectric actuators integrated with nanowires, can be employed for real-time  $E_g$  and SS tuning, which may be a potential scheme for harmonizing multiple conflicting parameters in TFET device physics [73–75]. In summary, these prospects highlight the potential of heteroepitaxial nanowire TFETs to transcend Boltzmann limits and promote its further

compatibility and even replacement of current CMOS transistors while addressing scalability and energy efficiency demands for post-Moore electronics.

#### 4 | Novel Tunnel Junctions Based on 2D Materials

The exceptional electronic characteristics of low-dimensional semiconductors have positioned them as pivotal components in advancing transistor technologies, particularly TFETs, over the

past decade. 2D materials offer distinct advantages over conventional 3D semiconductors, including atomic-scale thickness, tunable layer-dependent band structures, and superior charge carrier transport properties [76]. These attributes directly address fundamental limitations inherent to bulk semiconductor devices. The crystalline lattice of layered materials features robust in-plane covalent bonding contrasted by weak interlayer vdW interactions, enabling mechanical exfoliation of atomically thin sheets while preserving intrinsic electronic qualities. Crucially, the energy-momentum dispersion relations exhibit significant variation across monolayer, few-layer, and bulk configurations, permitting precise modulation of electronic behavior through external stimuli such as electric fields, strain, or magnetic fields.

The atomic confinement of charge carriers within 2D channels enhances electrostatic gate control by minimizing body thickness ( $t_{\text{body}}$ ), thereby suppressing SCEs through geometric screening length ( $\lambda$ ) reduction. This scaling parameter  $\lambda$ , inversely proportional to both equivalent oxide thickness (EOT) and  $t_{\text{body}}$ , governs critical performance metrics: it dictates the minimum viable gate length ( $L_g$ ) for maintaining electrostatic integrity, influences Schottky barrier formation at metal-semiconductor interfaces, and modulates BTBT probabilities. The vdW heterostructure architecture eliminates interfacial defects common in conventional semiconductors, circumventing mobility degradation from dangling bonds while ensuring atomic-level thickness uniformity for abrupt band edge transitions essential for efficient tunneling.

These intrinsic properties collectively address two persistent challenges in 3D TFET implementations: achieving atomically sharp tunneling junctions and maintaining gate dominance in aggressively scaled devices [77, 78]. Material diversity within the 2D family enables tailored device engineering through heterojunction design—including homojunctions, mixed-dimensional hybrids, and all-2D vertical stacks—with performance metrics dictated by specific material parameters such as bandgap magnitude, carrier effective mass, and dielectric screening. Strategic band structure engineering combined with advanced fabrication techniques facilitates optimized tunneling efficiency, potentially realizing steep SS below the Boltzmann limit alongside high drive currents [79]. Current research focuses on exploiting these material-specific properties through innovative device architectures and contact engineering to overcome remaining challenges in contact resistance and tunneling probability optimization [80].

#### 4.1 | 2D-Material Homojunctions: Obstacles and Opportunities

At the very beginning, thanks to the outstanding electrostatic performance of 2D materials, homojunctions based on single 2D materials like graphene and MoS<sub>2</sub> were designed and constructed through a segmented gate-voltage modulation strategy. Unfortunately, homogeneous tunneling junctions based on single 2D material cannot meet the requirements on all key parameters for constructing a high-performance TFET. For example, 2D semiconductors with flexible band-controllability such as TMDs do not have competitive ultra-low  $m^*$ , and

graphene that can meet the  $m^*$  requirement is difficult to achieve uniform and efficient bandgap regulation. As a result, the experimental performance of TFETs in this category generally needs more significant improvement. Therefore, in this section, we will focus on the innovative structure research of relevant tunneling junctions: they are either based on device model simulation, or they are slightly deformed structures, which are not strictly homogeneous junctions. We still believe that this kind of TFET has great development potential, because the homojunction can naturally show a defect-free tunnel junction, which is one of the necessary factors for high-performance TFETs.

Initial explorations of 2D material-based TFETs leveraged the superior electrostatic integrity of homojunction architectures employing materials like graphene and TMDs. These mono-material-based tunneling configurations, however, face intrinsic material limitations in simultaneously achieving critical performance metrics. Graphene's exceptional carrier mobility stems from its remarkably low effective mass ( $m^* \approx 0.033m_0$ ), a critical parameter for high-performance tunnel junctions [81, 82]. While graphene benefits from its massless Dirac fermion behavior near the  $K$ -point offers exceptional transport characteristics, its inherent zero bandgap fundamentally restricts tunneling efficiency. Conversely, TMDs demonstrate gate-tunable bandgaps but suffer from comparatively higher  $m^*$  values that limit tunneling probability [83, 84]. This material-level tradeoff has driven innovations in structural engineering to circumvent inherent limitations. For example, symmetry-breaking mechanisms under vertical bias have emerged as critical enablers for graphene-based TFETs. Bilayer graphene exhibits electrically tunable bandgap opening through controlled interlayer potential asymmetry, achieved via dual-gate architectures with spatially separated gate electrodes (Figure 5A) [85]. Computational studies demonstrate that differential biasing of partially overlapping top and bottom gates induces both channel bandgap modulation and doping gradient formation across source-channel-drain regions (Figure 5B-D). This configuration enables simultaneous optimization of tunneling window and carrier injection efficiency [87]. Experimental implementations further enhance this asymmetry through surface charge transfer doping, where physisorbed F<sub>4</sub>TCNQ molecules create interlayer charge imbalance, amplifying the vertical electric field's bandgap-opening effect (Figure 5D) [85]. Contact engineering through work-function-tailored electrodes complements this approach by enabling Fermi level alignment without conventional impurity doping [88]. The design of effective contact structures in 2D materials often involves both the edge and top surface due to the significant surface-to-edge area ratio of the contact [89]. In addition to enhancing edge contacts, overall contact performance can be improved by reducing the tunnel barriers specifically at the top surface. This can be effectively realized through the hybridization of interfacial metal atoms (e.g., Ti) [90] or emerging 2D semimetals (e.g., graphene) [91] with the surface atoms of 2D semiconductors. Prior research provides a well-established framework for achieving low-resistance Ohmic contacts on 2D semiconducting surfaces using this surface hybridization approach.

Beyond graphene, materials with balanced  $m^*$  and bandgap characteristics show promise. TFETs based on MoTe<sub>2</sub> demonstrates enhanced performance in hetero-stack configurations combining few-layer channels with graphene gate electrodes and hexagonal

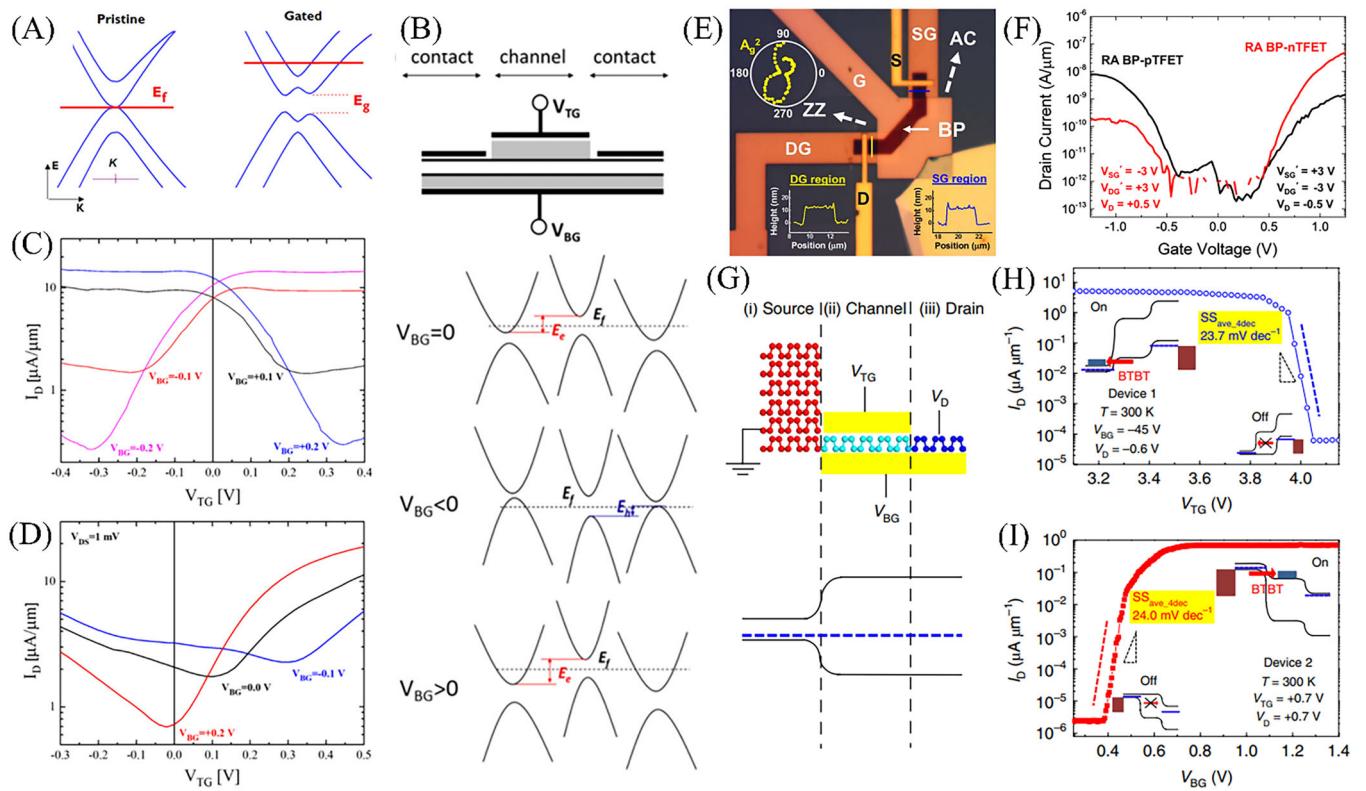

**FIGURE 5** | Transport engineering in homo-junctional 2D TFETs. (A) Energy dispersion relations of intrinsic graphene under neutral conditions versus electrostatically gated configurations. (B) Architectural schematic and equilibrium/nonequilibrium band alignment for dual-gated graphene FET incorporating doped source/drain electrodes. (C) Modulated transfer characteristics for undoped devices with back-gate potential swept between  $-0.2$  and  $+0.2$  V. (D) Modulated transfer characteristics under surface charge transfer doping via F<sub>4</sub>TCNQ molecular layers, demonstrating gate-tunable behavior at back-gate voltage ( $V_{BG}$ ) =  $+0.2$ ,  $0$ , and  $-0.1$  V, respectively. (A–D) Reproduced with permission [85]. Copyright 2014, IOP Publishing. (E) Planar microscopy visualization of right-angle BP tunneling FET architecture, accompanied by topographic atomic force microscopy line profiles at charge injection interfaces and polarization-dependent Raman spectroscopy signatures. (F) Ambipolar transport characteristics for p-type (black) and n-type (red) BP-TFET operation under symmetric source-drain bias configurations ( $V_{DD} = \pm 5$  V). (E, F) Reproduced with permission [86]. Copyright 2019, IEEE. (G) Hetero-structured BP tunnel junction illustrating layer-dependent band alignment across three functional zones: (i) heavily doped source, (ii) electrostatically modulated channel, and (iii) drain with field-induced band-shift. Color gradients represent doping concentration variations. (H) p-channel switching characteristics at  $V_{DD} = -0.6$  V exhibiting  $0.15$  V threshold gate swing for current modulation. (I) n-channel operation at  $V_{DD} = +0.7$  V requiring  $0.2$  V back-gate actuation for ON/OFF transition. Inset: band engineering through coordinated  $V_{BG}$ ,  $V_{TG}$  (top-gate voltage), and  $V_{DD}$  manipulation enables precise control over inter-band tunneling conditions ( $\Delta\varphi > 0$  for BTBT activation vs. blockade in off-state). (G–I) Reproduced with permission [36]. Copyright 2020, Springer Nature.

boron nitride (*h*-BN) dielectrics [35]. These devices achieve sub-60 mV dec<sup>-1</sup> switching characteristics through optimized band alignment and reduced  $D_{it}$ . In addition to MoTe<sub>2</sub>, BP emerges as a particularly versatile candidate due to its thickness-dependent direct bandgap (0.3–2 eV) and anisotropic effective mass ( $m_{T_{\text{armchair}}}^* \approx 0.1m_0$  vs.  $m_{T_{\text{zigzag}}}^* \approx 0.15m_0$ ) [92–94]. According to this characteristic, researchers designed in-plane biaxial TFET, which shows good application potential (Figure 5E,F) [86]. Such advance also positions anisotropic 2D materials as viable platforms for post-CMOS steep-slope devices. On the other hand, a monolayer-to-bulk BP TFET architecture exemplifies another flexibility: bulk BP in the source region enhances band-to-band tunneling efficiency, while monolayer BP in the channel/drain regions suppresses ambipolar conduction through widened bandgaps (Figure 5G) [36]. As a result, vertical BP TFETs achieve sub-thermal switching (26 mV dec<sup>-1</sup> over 5 current decades) by decoupling source doping control from channel electrostatics via independent dual-gate addressing (Figure 5H,I). These architectural innovations highlight two key design principles: (1) Spatial

separation of bandgap engineering and carrier transport pathways enables independent optimization of tunneling probability and electrostatic control. (2) Anisotropy engineering through crystallographic alignment and thickness grading allows access to favorable transport directions and effective mass minimization [95–97]. While current experimental implementations still face challenges in achieving simultaneously high  $I_{60}$  (as least  $1\ \mu\text{A}\ \mu\text{m}^{-1}$  is required) and sub-60 mV dec<sup>-1</sup> operation across wide current ranges of more than 4 orders of magnitudes, the fundamental compatibility of these designs with scalable vdW integration suggests substantial potential for performance scaling through multilayer stacking and contact resistance reduction strategies.

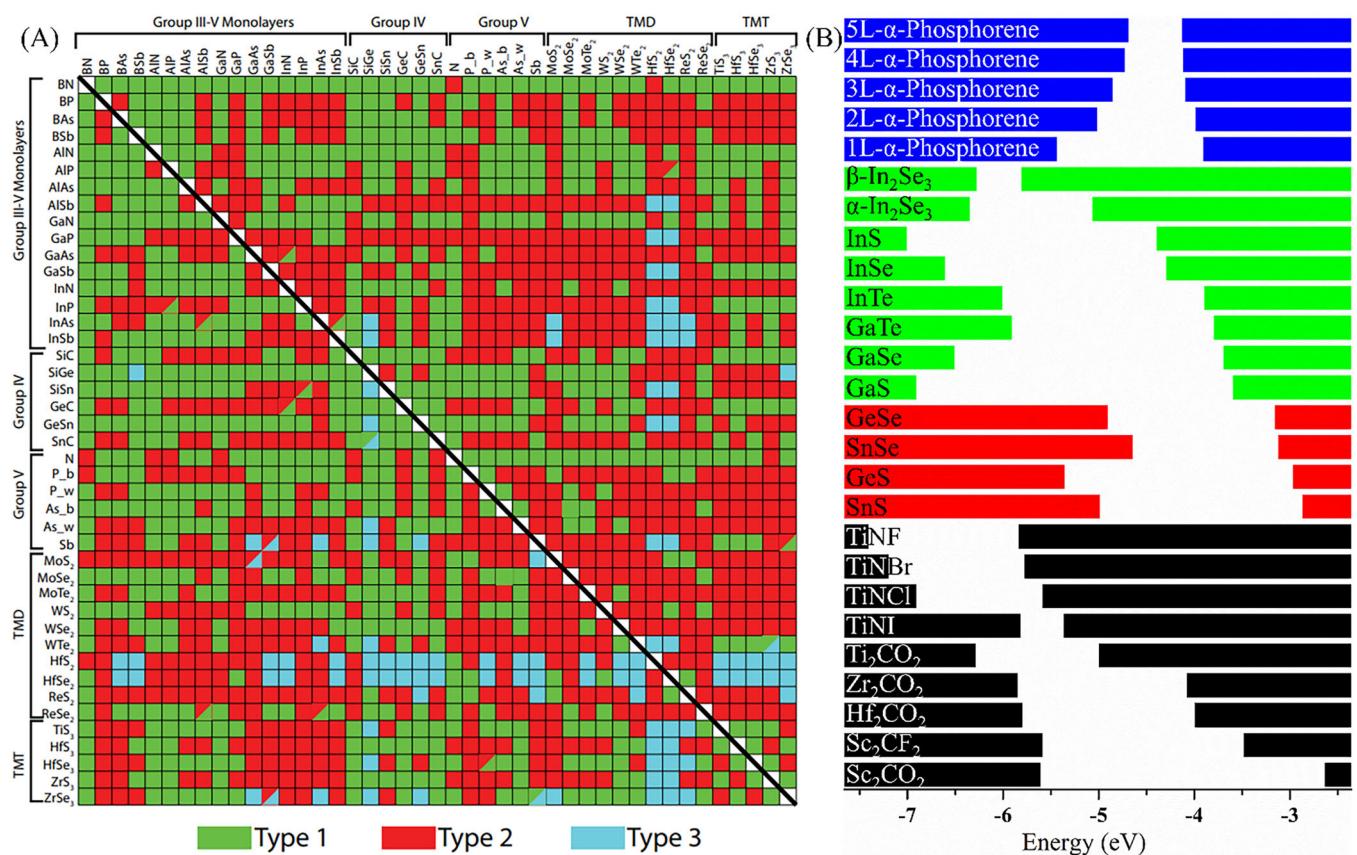

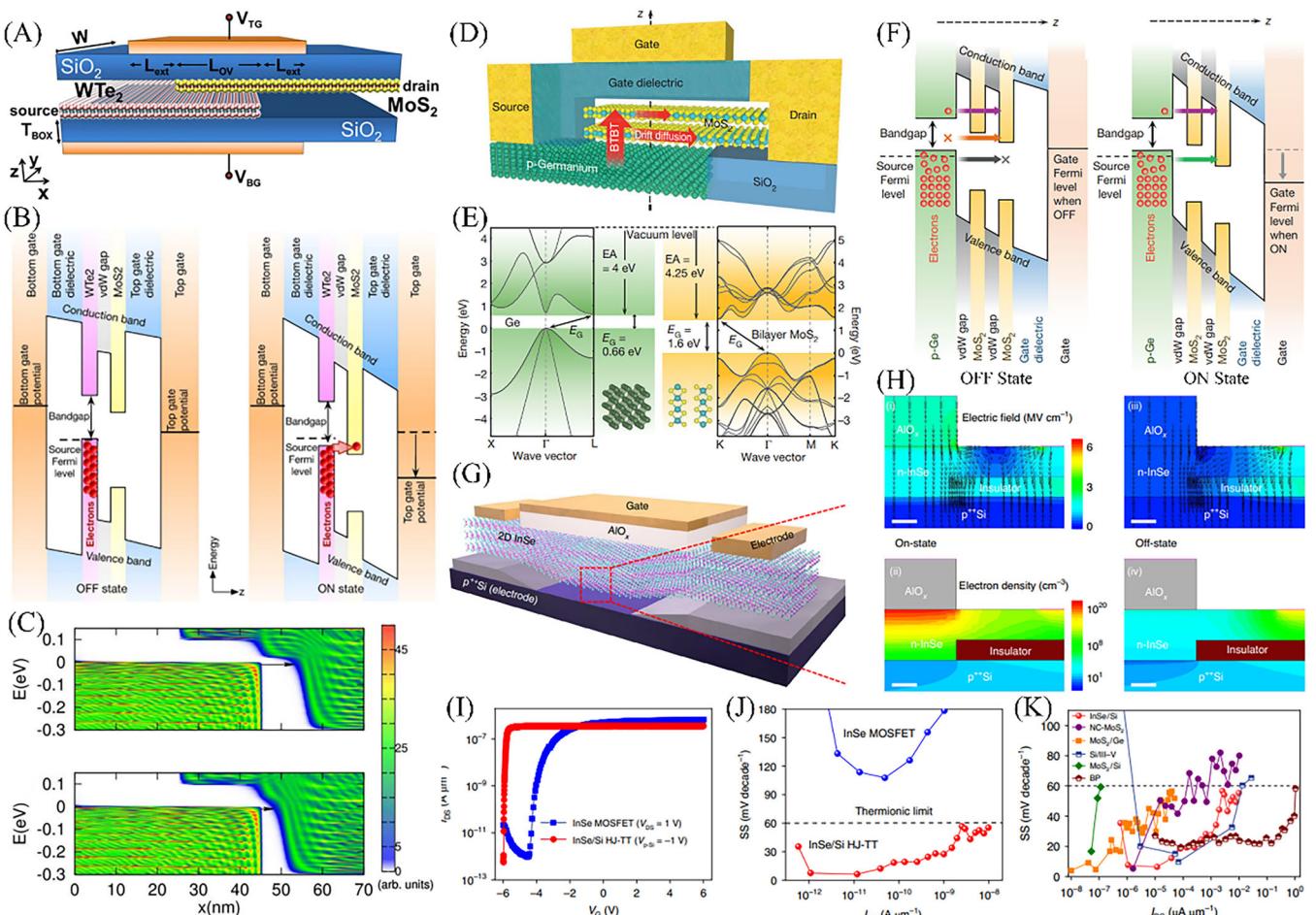

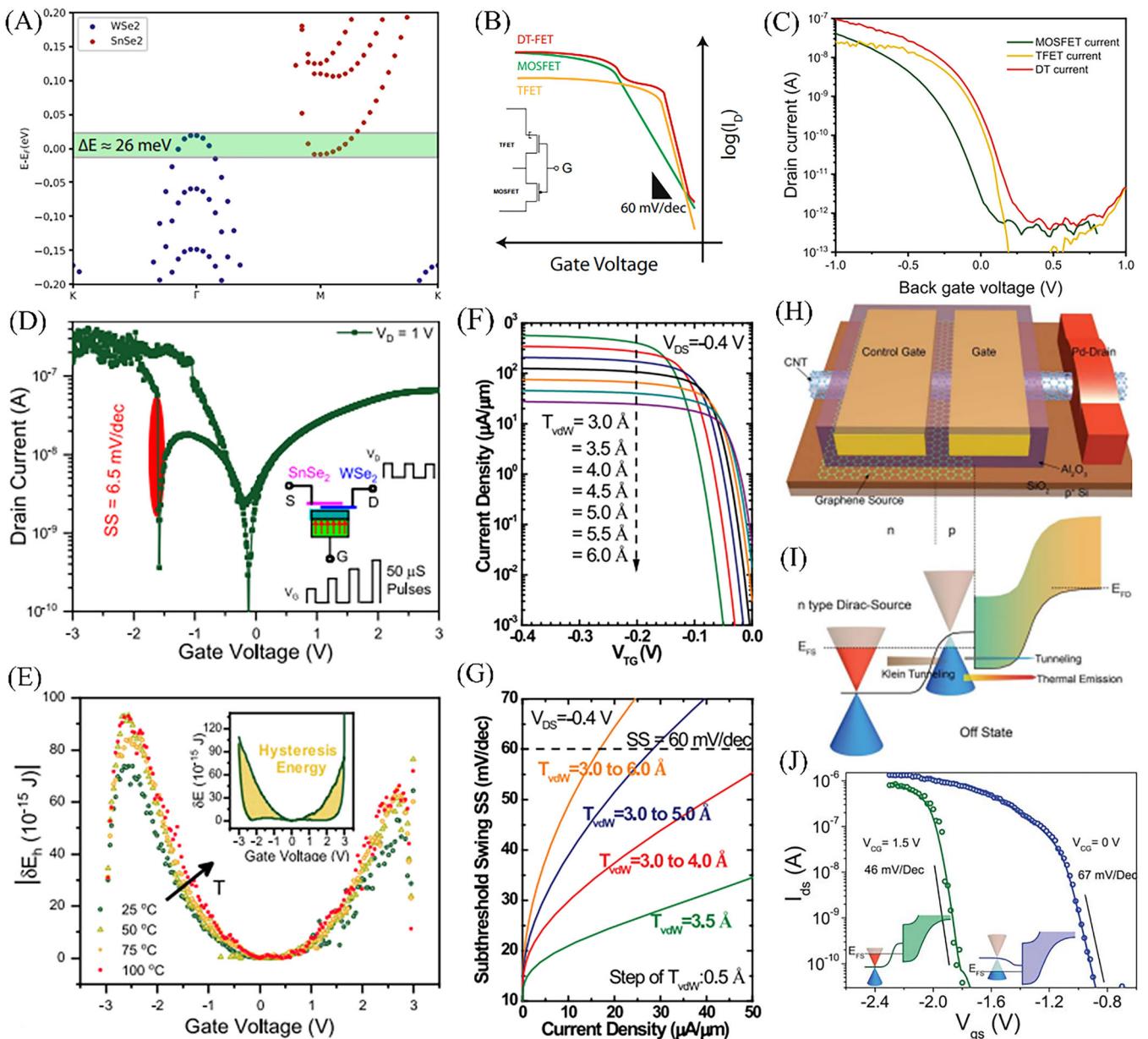

#### 4.2 | Vertical vdW Heterojunctions: Great Potential

Vertical vdW heterostructures present transformative opportunities for tunneling device engineering through atomic-scale