RESEARCH ARTICLE | JULY 11 2017

## High-performance pentacene OTFT by incorporating Ti in LaON gate dielectric *⊙*

Y. X. Ma (10); C. Y. Han; W. M. Tang; P. T. Lai

Appl. Phys. Lett. 111, 023501 (2017) https://doi.org/10.1063/1.4993157

## Articles You May Be Interested In

Improved interfacial and electrical properties of Ge MOS capacitor by using TaON/LaON dual passivation interlayer

Appl. Phys. Lett. (July 2016)

Improved electrical properties of Ge metal-oxide-semiconductor capacitors with high- k HfO 2 gate dielectric by using La 2 O 3 interlayer sputtered with/without N 2 ambient

Appl. Phys. Lett. (July 2010)

Field-effect transistors with LaAlO 3 and LaAlO x N y gate dielectrics deposited by laser molecular-beam epitaxy

Appl. Phys. Lett. (October 2004)

## High-performance pentacene OTFT by incorporating Ti in LaON gate dielectric

Y. X. Ma, 1 C. Y. Han, 2 W. M. Tang, 3 and P. T. Lai 1

<sup>1</sup>Department of Electrical and Electronic Engineering, The University of Hong Kong, Pokfulam Road, Hong Kong Island 999077, Hong Kong

<sup>2</sup>School of Microelectronics, Xi' an Jiao Tong University, Xi' an 710049, China

(Received 22 February 2017; accepted 26 June 2017; published online 11 July 2017)

Pentacene organic thin-film transistors (OTFT) using high-k LaTiON gate dielectric with different Ti contents are investigated. The  $La_xTi_{(1-x)}ON$  films (with x=1,0.87,0.76, and 0.67) are deposited by reactive sputtering followed by an annealing in  $N_2$  at 200 °C. The OTFT with  $La_{0.87}Ti_{0.13}ON$  can achieve a high carrier mobility of  $2.6 \, \mathrm{cm}^2/\mathrm{V} \cdot \mathrm{s}$ , a small threshold voltage of  $-1.5 \, \mathrm{V}$ , a small sub-threshold swing of 0.07 V/dec, and a small hysteresis of 0.17 V. AFM and X-ray photoelectron spectroscopy reveal that Ti can suppress the hygroscopicity of La oxide to achieve a smoother dielectric surface, which can result in larger pentacene grains and thus higher carrier mobility. All the devices show a clockwise hysteresis because both the LaOH formation and Ti incorporation can generate acceptor-like traps in the gate dielectric. *Published by AIP Publishing*. [http://dx.doi.org/10.1063/1.4993157]

Owing to their potential applications in flexible devices such as large-area flexible displays and flexible sensors, organic thin-film transistors (OTFTs) have been extensively studied recently. Although the characteristics of OTFTs have been deeply explored in the past, the performance and operating voltage of OTFTs still require further improvements. Pentacene OTFTs with gate dielectric like SiO<sub>2</sub> or PMMA could achieve high carrier mobility (~1 cm²/V s) but with a relatively large threshold voltage (>5 V). Thinner dielectric film can reduce the operating voltage at the expense of higher

relatively large threshold voltage (>5 V).<sup>3,4</sup> Thinner dielectric film can reduce the operating voltage at the expense of higher gate leakage current. Therefore, to achieve both low leakage current and small threshold voltage, high-k dielectric materials need to be employed. The performance of OTFT strongly depends on the quality of high-k dielectrics. Researchers have explored various high-k dielectric materials for use in pentacene OTFTs and their carrier mobility varied from 0.031 to 1.14 cm<sup>2</sup>/V·s.<sup>5,6</sup> Recently, it has been reported the addition of elements such as Nb and Zr could suppress the hygroscopicity of La-based oxides and improve their k-value. LaHfO and LaNbO were used as gate dielectric for high-performance pentacene OTFTs, which showed high carrier mobility, small threshold voltage, small hysteresis, and small sub-threshold swing (SS).<sup>6,7</sup> Ti incorporation in gate dielectric has been explored in the

Ti incorporation in gate dielectric has been explored in the past years due to the extremely high k value of Ti oxide ( $\sim 80$ ). However, due to the small bandgap of TiO<sub>2</sub> ( $\sim 3.2 \,\mathrm{eV}$ ), Ti incorporation could increase gate leakage and introduce traps into the hybrid dielectric. On the other hand, although La<sub>2</sub>O<sub>3</sub> has a larger band gap ( $\sim 6 \,\mathrm{eV}$ ), it is hygroscopic, thus easily forming hydroxide with moisture. As a result, incorporation of Ti in La oxide allows the two metal elements to complement each other: La can greatly passivate the traps in TiO<sub>2</sub> while Ti can suppress the hygroscopicity of La oxide and increase its k-value. Therefore, in this work, with an attempt to combine the advantages of La<sub>2</sub>O<sub>3</sub> and TiO<sub>2</sub>, La<sub>x</sub>Ti<sub>(1-x)</sub>ON films with different Ti contents are prepared by sputtering and used

as the gate dielectric of pentacene OTFT. With a Ti content (1-x) of 13%, high-performance pentacene OTFT with high carrier mobility and small threshold voltage can be obtained.

Initially, the standard RCA method was applied to clean the silicon wafers (n<sup>+</sup>-type,  $\langle 100 \rangle$ , resistivity = 0.005  $\Omega$ ·cm) followed by dipping the wafers in 5% hydrofluoric acid to remove the native oxide on the silicon surface. Then, 40-nm La<sub>x</sub>Ti<sub>(1-</sub> <sub>x)</sub>ON (with x = 1, 0.87, 0.76, and 0.67) films were deposited on the wafers as gate dielectric by a sputterer (Denton Vacuum LLC Discovery 635) in an Ar/O<sub>2</sub>/N<sub>2</sub> ambient. La<sub>2</sub>O<sub>3</sub> and Ti targets were co-sputtered with a RF power of 30 W for La<sub>2</sub>O<sub>3</sub> and different DC currents (0, 0.04, 0.07, and 0.10 A) for Ti (denoted as samples A, B, C, and D, respectively). The flow rate of Ar/ O<sub>2</sub>/N<sub>2</sub> was fixed at 24:3:6 sccm during the deposition. Then, annealing at 200 °C was carried out for all the samples in N<sub>2</sub> for 20 min. Next, 40-nm pentacene (99% purity, purchased from Luminescene Technology Corp.) was deposited on the dielectrics by an evaporator (Angstrom Engineering Nexdep) at a pressure of  $4.9 \times 10^{-6}$  Torr, with the substrate at room temperature. The deposition rate was 1.2 nm/min monitored by a quartzcrystal oscillator. Finally, gold was evaporated on the pentacene film to form source and drain electrodes by using a shadow mask with a channel of  $100 \, \mu \text{m}$  in width and  $40 \, \mu \text{m}$  in length.

The gate-dielectric capacitance per unit area ( $C_{ox}$ ) of the OTFTs was obtained by measuring capacitors fabricated by lithography method with a structure of Al/La<sub>x</sub>Ti<sub>(1-x)</sub>ON/n<sup>+</sup>Si using HP 4284A precision LCR meter. The I-V characteristics of the OTFTs were measured by HP 4145B semiconductor parameter analyzer. The dielectric thickness ( $t_{ox}$ ) was determined by a Wvase 32 ellipsometer. All measurement processes were carried out in air at room temperature. The surface morphologies of the dielectric and pentacene films were measured by a Veeco multi-mode scanning probe microscope while X-ray photoelectron spectroscopy (XPS) was applied to analyze the physical properties of the dielectric films.

<sup>&</sup>lt;sup>3</sup>Department of Applied Physics, The Hong Kong Polytechnic University, Hung Hom 999077, Hong Kong

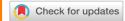

FIG. 1. XPS spectrum of O 1s for  $La_xTi_{(1-x)}ON$  film with: (a) x=1, (b) x=0.87, (c) x=0.76, and (d) x=0.67.

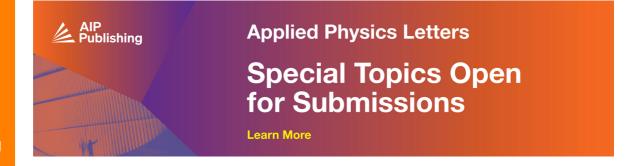

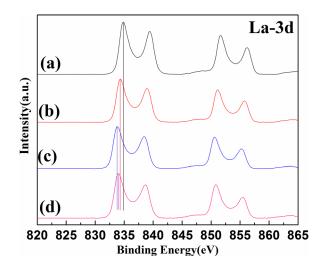

XPS results show that the atomic ratio of La/(La + Ti) is 100%, 87%, 76%, and 67% for samples A, B, C, and D, respectively. Figure 1 is the XPS spectrum of O 1s for the dielectric films with different Ti contents. The binding energy for La-O, La-OH and Ti-O is 529.1 eV, 531.3 eV, and 529.8 eV, respectively. According to Fig. 1, it is clear that sample A without Ti-incorporation has the largest amount of La-OH bonds due to the absorption of the moisture in the air. With increasing Ti content in the dielectric, the amount of La-OH is reduced significantly. In the XPS spectrum of Ti 3p shown in Fig. 2, the binding energy of the peak shifts to higher value from sample B to sample D with increasing Ti content because owing to the higher electronegativity of Ti (1.54) than La (1.1), increasing the Ti content can generate more oxygen vacancies as acceptor-like traps. In the XPS

spectrum of La 3d shown in Fig. 3, the binding energy of the peak first shifts to lower value from sample A to sample C with increasing Ti content, supporting the hygroscopicity suppression by Ti incorporation. However, the peak of sample D moves back to higher energy, further supporting the generation of oxygen vacancies by the Ti incorporation.

Surface roughness is a key factor in affecting the pentacene growth and thus device performance. Smoother surface has fewer nucleation sites for pentacene growth to result in larger pentacene grains and thus higher carrier mobility. La oxide can absorb the moisture in the air to expand non-uniformly, thus producing a rougher surface. <sup>11</sup> The incorporation of Ti can reduce the hygroscopicity of La oxide (see the XPS spectrum in Fig. 1), and thus the surface roughness

FIG. 2. XPS spectrum of Ti 3p for  $La_xTi_{(1-x)}ON$  film with: (a) x=0.87, (b) x=0.76, and (c) x=0.67.

FIG. 3. XPS spectrum of La 3d for the samples  $La_xTi_{(1-x)}ON$  film with: (a) x=1, (b) x=0.87, (c) x=0.76, and (d) x=0.67.

TABLE I. Main parameters of pentacene OTFTs with different Ti contents.

| Sample                                     | A                     | В                     | C                     | D                    |

|--------------------------------------------|-----------------------|-----------------------|-----------------------|----------------------|

| La/(Ti+La) (%)                             | 100                   | 87                    | 76                    | 67                   |

| $\mu  (\text{cm}^2/\text{V}\cdot\text{s})$ | 1.9                   | 2.6                   | 2.1                   | 1.1                  |

| $V_{T}(V)$                                 | -1.6                  | -1.5                  | -1.3                  | -0.96                |

| $\Delta V_{T}(V)$                          | 0.37                  | 0.17                  | 0.76                  | 0.93                 |

| SS (V/dec)                                 | 0.10                  | 0.07                  | 0.13                  | 0.30                 |

| $N_t (\mathrm{cm}^{-2} \mathrm{eV}^{-1})$  | $8.9 \times 10^{11}$  | $2.6 \times 10^{11}$  | $2.0 \times 10^{12}$  | $7.6 \times 10^{12}$ |

| $I_d(\mu A)$ at $V_D = -3 V$ ,             | 4.88                  | 6.67                  | 7.68                  | 5.6                  |

| $V_G = -5 \ V$                             |                       |                       |                       |                      |

| $I_{off}(A)$                               | $3.5 \times 10^{-11}$ | $1.1 \times 10^{-11}$ | $6.6 \times 10^{-11}$ | $1.2 \times 10^{-9}$ |

| On/off current ratio                       | $1.4 \times 10^{5}$   | $6.1 \times 10^{5}$   | $1.1 \times 10^{5}$   | $0.05 \times 10^{5}$ |

| $C_{ox} (\mu F/cm^2)$                      | 0.21                  | 0.24                  | 0.27                  | 0.30                 |

| $t_{ox}$ (nm)                              | 42                    | 40                    | 43                    | 43                   |

| k                                          | 10                    | 11                    | 13                    | 14                   |

| Dielectric roughness (nm)                  | 0.60                  | 0.35                  | 0.34                  | 0.31                 |

of the dielectric, as supported by the roughness values measured by AFM shown in Table I. All the three samples with Ti incorporation have smaller dielectric-surface roughness than sample A with pure LaON as gate dielectric, and the surface roughness decreases with increasing Ti content due to lower hygroscopicity of the dielectric. Since the highest processing temperature was only 200 °C [much lower than the crystallization temperatures of TiO<sub>2</sub> (above 600 °C in rutile phase and 350 °C in anatase phase) and La<sub>2</sub>O<sub>3</sub> (400 °C)<sup>14,15</sup>] and nitrogen incorporation can raise crystallization temperature, <sup>16,17</sup> oxide crystallization should have little effect on the surface roughness.

The AFM images of 40-nm pentacene films deposited on the dielectric films are shown in Fig. 4. The pentacene grain size first increases with Ti incorporation but then decreases as Ti content further increases. This phenomenon

FIG. 4. AFM image  $(5 \mu m \times 5 \mu m)$  of pentacene film on  $La_x Ti_{(1-x)}ON$ : (a) sample A with x = 1, (b) sample B with x = 0.87, (c) sample C with x = 0.76, and (d) sample D with x = 0.67.

could be explained as follows. As mentioned earlier, Ti incorporation can suppress the hygroscopicity of La oxide to produce a smoother dielectric surface, thus resulting in larger pentacene grains grown on the dielectric. However, with increasing Ti content, the dielectric has more Ti-related traps, which provide more nucleation sites, thus leading to smaller pentacene grains. Smaller pentacene grains increase the grain-boundary-induced scattering on charge carriers and so reduce the carrier mobility. This relation will be later supported by the electrical characteristics of the OTFT's.

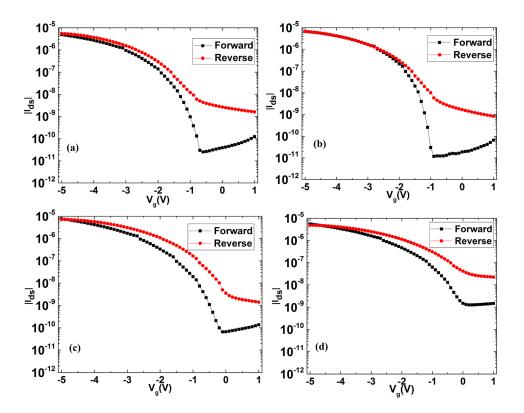

The transfer characteristics of the OTFTs are shown in Fig. 5. The forward (off-to-on) sweep is measured from +1 V to -5 V and the reverse (on-to-off) sweep is measured from -5 V to +1 V. The pause time between the two sweeps is negligible. Hysteresis  $\Delta V_T$  is defined as  $V_T$  of reverse sweep minus that of the forward sweep. For field-effect transistors, carrier mobility and threshold voltage are important parameters to judge its performance.

The carrier mobility  $\mu$  is the average charge-carrier drift velocity per unit electric field. In the saturation regime of p-type OTFT and based on formula (1), the carrier mobility can be obtained as (2),  $^{20,21}$  where  $C_{ox}$  is the dielectric capacitance per unit area,  $I_d$  the saturation current,  $V_T$  the threshold voltage, W the channel width, L the channel length, and  $V_G$  the voltage applied to the gate electrode. Therefore, the carrier mobility can be extracted from the slope of the linear region in the curve  $\sqrt{I_d}$  versus  $V_G$

$$I_d = -\frac{WC_{ox}\mu}{2L}(V_G - V_T)^2,$$

(1)

$$\mu = \frac{2L}{WC_{or}} \left( \frac{\partial \sqrt{I_d}}{\partial V_G} \right)^2. \tag{2}$$

The subthreshold swing (SS) is to measure the speed of device switching between OFF-state and ON-state in the region of exponential  $I_d$  increase with  $V_G$ , and defined as

$$SS = \frac{dV_G}{d(\log_{10} I_d)}. (3)$$

Its value is extracted by fitting 3 points on the steepest part of the curve (excluding the point with the lowest current, i.e., off current  $I_{\rm off}$ ). Assuming that the densities of deep bulk trap and deep interface trap are independent of trap energy, the trap density at/near the pentacene/dielectric interface ( $N_t$ ) can be calculated from SS as

$$Nt = \frac{Cox}{e} \left( \frac{e \times SS}{kT \ln 10} - 1 \right),\tag{4}$$

where e is the electron charge and T the absolute temperature.

The main parameters of the samples extracted from their  $I_d$  vs.  $V_G$  curve are summarized in Table I, where the values are the median values based on about 20 devices. Sample B (with  $La_{0.87}Ti_{0.13}ON$  as gate dielectric) exhibits the highest carrier mobility of  $2.6 \, \text{cm}^2/\text{V} \cdot \text{s}$ , which is about 1.4 times higher than that of sample A with pure LaON as gate dielectric. This should be due to its largest pentacene grain size (see Fig. 4), which is attributed to (1) smoother dielectric

FIG. 5. Transfer characteristics of the OTFTs: (a) sample A, (b) sample B, (c) sample C, and (d) sample D.

surface (see Table I) induced by the Ti incorporation, (2) little traps generated by light Ti incorporation as supported by smallest N<sub>t</sub> in Table I. The SS values of sample A and sample B are 0.10 V/dec and 0.07 V/dec, respectively, with the former larger than the latter by 30%. The samples C and D show a SS of 0.13 V/dec and 0.30/dec, respectively. Owing to the improved dielectric quality, sample B also has the smallest SS and  $\Delta V_T$ . With higher Ti incorporation in samples C and D, the hygroscopicity of their gate dielectrics is further suppressed, resulting in less non-uniform dielectric expansion and thus a smoother dielectric surface, as supported by the surface roughness in Table I. However, the Tirelated traps also increase as reflected by a larger SS value in Table I. Therefore, with increasing Ti content, the carrier mobility initially increases (due to larger pentacene grains and smoother dielectric surface) but then decreases because more generated traps can increase the trap-related carrier scattering and also cause smaller pentacene grains. Moreover, as shown in Table I, the threshold voltage decreases with increasing Ti content because the Ti incorporation increases the k value of the gate dielectric due to the high k-value of Ti oxide ( $\sim$ 80).

Hysteresis is due to the traps near the pentacene/dielectric interface. The change in threshold voltage ( $\Delta V_T$ ) due to hysteresis can be extracted from the forward and reverse sweeps of the transfer characteristics. In Fig. 5, all the samples exhibit a clockwise hysteresis. Sample A with LaON dielectric has a  $\Delta V_T = 0.37$  V, which should be attributed to hydroxyl ions (OH) formed by the hygroscopicity of La oxide, trapping electrons during the forward sweep. With increasing Ti content, the hysteresis first decreases but then increases. This should be due to the fact that the Ti incorporation suppresses the hygroscopicity of La oxide and thus the formation of hydroxyl ions. However, further increase in Ti content could generate more Ti-related acceptor-like traps,

thus resulting in an increase of hysteresis. <sup>10</sup> Due to the hygroscopicity of La oxide, LaOH is formed with OH as acceptor-like trap, which can become negatively charged after capturing an electron in the dielectric. During the off-to-on sweep, electrons are injected from the gate electrode into the dielectric and captured by the acceptor-like traps in the dielectric. Upon the on-to-off sweep, some trapped electrons still remain in the dielectric, and so produce a shift of the threshold voltage in the positive direction.

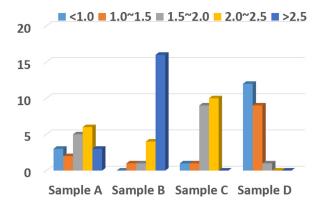

Figure 6 shows the carrier-mobility distribution, and the colors represent the ranges of mobility value while the height indicates the quantity of corresponding devices. It is obvious that the uniformity of sample A (with pure LaON) is the worst among all the samples due to the strongest moisture absorption and subsequent non-uniform expansion of its relevant dielectric film. Moreover, sample B statistically shows the highest carrier mobility.

This work has explored pentacene OTFT using  $La_x Ti_{(1-x)}$  ON as high-k gate dielectric with different Ti contents. The dielectric films were deposited by co-sputtering of Ti and

FIG. 6. Carrier-mobility distribution of the OTFTs.

La<sub>2</sub>O<sub>3</sub> targets in an Ar/O<sub>2</sub>/N<sub>2</sub> ambient. The Ti incorporation in La oxide can suppress its hygroscopicity to produce a smoother dielectric surface and thus larger pentacene grains, which can improve the carrier mobility. However, with increasing Ti content, Ti-related acceptor-like trap increases to reduce the carrier mobility. Therefore, by varying the Ti content in the gate dielectric, the pentacene OTFT with La<sub>x</sub>Ti<sub>(1-x)</sub>ON around x = 0.87 as dielectric can achieve the highest carrier mobility  $(2.6\,\mathrm{cm}^2/\mathrm{V}\cdot\mathrm{s})$ , the smallest *SS*  $(0.07\,\mathrm{V/dec})$  and smallest hysteresis  $(\Delta\mathrm{V_T} = 0.17\,\mathrm{V})$ .

We would like to acknowledge the Small Project Grant (201409176206), Seed Fund for Strategic Research Theme on New Materials and University Development Fund (Nanotechnology Research Institute, 00600009) of the University of Hong Kong.

- <sup>1</sup>H. Klauk, "Organic thin-film transistors," Chem. Soc. Rev. **39**(7), 2643–2666 (2010).

- <sup>2</sup>T. W. Kelley, P. F. Baude, C. Gerlach, D. E. Ender, D. Muyres, M. A. Haase, D. E. Vogle, and S. D. Theiss, "Recent progress in organic electronics: Materials, devices, and processes," Chem. Mater. 16, 4413–4422 (2004).

- <sup>3</sup>J. Roh, C. M. Kang, J. Kwak, C. Lee, and B. J. Jung, "Overcoming tradeoff between mobility and bias stability in organic field-effect transistors according to the self-assembled monolayer chain lengths," Appl. Phys. Lett 104, 173301 (2014).

- <sup>4</sup>W. Wang, J. Han, J. Ying, and W. Xie, "MoO<sub>3</sub> modification layer to enhance performance of pentacene-OTFTs with various low-cost metals as source/drain electrodes," IEEE Trans. Electron Devices **61**(10), 3507 (2014).

- <sup>5</sup>C. Y. Han, L. Qian, C. H. Leung, C. M. Che, and P. T. Lai, "High-performance pentacene thin-film transistor with ZrLaO gate dielectric passivated by fluorine incorporation," Org. Electron. **14**(11), 2973–2979 (2013).

- <sup>6</sup>C. Y. Han, W. M. Tang, C. H. Leung, C. M. Che, and P. T. Lai, "High-performance pentacene thin-film transistor by using LaNbO as gate dielectric," Appl. Phys. Lett. **107**, 033503 (2015).

- <sup>7</sup>M. F. Chang, P. T. Lee, S. P. McAlister, and A. S. Chin, "Small-subthreshold-swing and low-voltage flexible organic thin-film transistors which use HfLaO as the gate dielectric," IEEE Electron Device Lett. **30**(2), 133 (2009).

- <sup>8</sup>N. Lu, H.-J. Li, J. J. Peterson, and D. L. Kwong, "HfTiAlO dielectric as an alternative high-K gate dielectric for the next generation of

- complementary metal-oxide-semiconductor devices," Appl. Phys. Lett. 90, 082911 (2007)

- <sup>9</sup>K. Madhusudan Reddy, S. V. Manorama, and A. Ramachandra Reddy, "Bandgap studies on anatase titanium dioxide nanoparticles," Mater. Chem. Phys. 78, 239–245 (2002).

- <sup>10</sup>H. X. Xu, J. P. Xu, C. X. Li, C. J. Chan, and P. T. Lai, "Impacts of Ti on electrical properties of Ge metal-oxide-semiconductor capacitors with ultrathin high-K LaTiON gate dielectric," Appl. Phys. A **99**, 903–906 (2010).

- <sup>11</sup>Y. Zhao, M. Toyama, K. Kita, K. Kyuno, and A. Toriumi, "Moisture-absorption-induced permittivity deterioration and surface roughness enhancement of lanthanum oxide films on silicon," Appl. Phys. Lett. 88, 072904 (2006).

- <sup>12</sup>L. X. Qian, P. T. Lai, and W. M. Tang, "Effects of Ta incorporation In La<sub>2</sub>O<sub>3</sub> gate dielectric of InGaZnO thin-film transistor," Appl. Phys. Lett. **104**, 123505 (2014).

- <sup>13</sup>C. Y. Han, W. M. Tang, C. H. Leung, C. M. Che, and P. T. Lai, "A study on La incorporation in transition-metal (Y, Zr, and Nb) oxides as gate dielectric of pentacene organic thin-film transistor," IEEE Trans. Electron Devices 62(7), 2313 (2015).

- <sup>14</sup>H. Sankur and W. Gunning, "Crystallization and diffusion in composite TiO<sub>2</sub>-SiO<sub>2</sub> thin films," J. Appl. Phys. 66(10), 4747 (1989).

- <sup>15</sup>B. Hunsche, M. Vergohl, and A. Ritz, "Investigation of TiO<sub>2</sub> based thin films deposited by reactive magnetron sputtering for use at high temperatures," Thin Solid Films **502**, 188–192 (2006).

- <sup>16</sup>M. Nieminen, M. Putkonen, and L. Niinisto, "Formation and stability of lanthanum oxide thin films deposited from  $\beta$ -diketonate precursor," Appl. Surf. Sci. 174, 155–165 (2001).

- <sup>17</sup>J. Q. Song, C. Y. Han, and P. T. Lai, "Comparative study of Nb<sub>2</sub>O<sub>5</sub>, NbLaO, and La<sub>2</sub>O<sub>3</sub> as gate dielectric of InGaZnO thin-film transistor," IEEE Trans. Electron Devices 63(5), 1928 (2016).

- <sup>18</sup>M. Voigt, J. Pflaum, and M. Sokolowski, "Growth morphologies and charge carrier mobilities of pentacene organic field effect transistors with RF sputterred aluminium oxide gate insulators on ITO glass," Phys. Status Solidi A 205(3), 449–460 (2008).

- <sup>19</sup>S. Verlaak, V. Arkhipov, and P. Heremans, "Modeling of transport in polycrystalline organic semiconductor films," Appl. Phys. Lett. 82(5), 745 (2003).

- <sup>20</sup>W. L. Kalb and B. Batlogg, "Calculating the trap density of states in organic field-effect transistors from experiment: A comparison of different methods," Phys. Rev. B 81, 035327 (2010).

- <sup>21</sup>G. Horowitz, "Organic field-effect transistors," Adv. Mater. 10, 365 (1998).

- <sup>22</sup>S. H. Kim, H. Yang, S. Y. Yang, K. Hong, D. Choi, C. Yang, D. S. Chung, and C. E. Park, "Effect of water in ambient air on hysteresis in pentacene field-effect transistors containing gate dielectrics coated with polymers with different functional groups," Org. Electron. 9, 673–677 (2008).