MATERIALS SCIENCE

## Selective nano-buckling improves the performance of graphene logic transistors

Tong Yang<sup>1</sup> and Ming Yang<sup>1,2,\*</sup>

The massive integration of silicon-based transistors into modern electronic devices greatly increases power consumption and heat generation/dissipation [1]. In this concern, transistors based on atomically-thin graphene that exhibit high electric and thermoelectric conductivities with negligible contact resistance, wide-range gate-tunability and high compatibility with existing processing technologies, have emerged as promising alternatives in the post-Moore era [2,3]. Due to its gapless band dispersion, however, graphene-based transistors show a limited on/off switching ratio (<100). Various methods such as doping [4], substrate engineering [5] and dimensional reduction [6] have been proposed, but almost none of them could reach a satisfying on/off ratio without sacrificing carrier mobility. Further graphene functionalization, dedicated device architectures and even external field regulation are still required.

Writing in National Science Review, a team led by Prof. Yanpeng Liu from Nanjing University of Aeronautics and Astronautics innovatively overcame this compromise between the on/off ratio and carrier mobility (Fig. 1). They proposed a novel device architecture based on a graphene/black phosphorus (BP) heterostructure that is peculiarly prone to nano-buckles on demand under local current-annealing. The as-fabricated graphene-based transistors show outstanding on/off ratios >10³ at room temperature while preserving intrinsic ultrahigh carrier mobility.

In the frame of electro-thermomechanical multiple fields coupling at

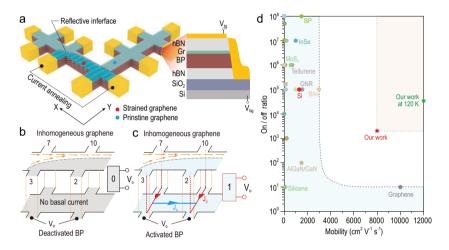

**Figure 1.** An illustration of the partially nano-buckled graphene transistor. (a) Schematic diagram of the graphene transistor. (b) Operation mechanism of graphene-based transistor. Inhomogeneous current flow within the graphene (Gr) channel when BP is insulating, representing Boolean '0' state. (c) Dual-channel propagations of graphene and BP bottom layer. Non-zero  $V_{\rm o}$  represents Boolean '1' state. (d) Room-temperature on/off ratio and carrier mobility of FETs based on various semi-conductors including metal oxides, transition metal dichalcogenides, and puckered semiconductors. Adapted from ref. [7].

the atomic scale, Prof. Liu and his coworkers first embarked on heavily lattice-mismatched heterostructures, for instance, a hexagonal graphene monolayer on orthogonal BP flakes, and selectively applied a direct current to thermally anneal graphene on puckered BP in between two electrodes. Upon global annealing, graphene/BP is likely to form a rotation-angle-dependent Moiré superlattice and pseudomagnetic field, accompanied with electron localization within circumscribed graphene landscapes [8]. Here, the annealed graphene/BP region locally buckles at the nanoscale with a ridge-like spatial structure (behaving as electron reflective interface) formed at the intersection with the adjacent un-annealed one. This electrical interface blocks the in-plane current flow and gives rise to an off-state in the logic transistors. For the on-state, the authors alternatively leverage a simple back-gate to make the BP bottom layer conductive thus generating dual-channel propagations of graphene and BP. In this manner, the logic operation of the graphene transistor is readily realized by low-power gate control, even at room temperature and intense magnetic fields.

Via electrostatic gating, the graphene-based transistor simultaneously generates an on/off ratio  $>10^3$  and a high mobility of  $\sim\!8000~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$  at room temperature, fulfilling the low-power criterion suggested by the International Roadmap for Devices and Systems [9]. This breakthrough not only sheds light on the control of two-dimensional electrons through nanoscale multiple-fields coupling, but also establishes a paradigm for the development of graphene-based transistors, edging us one step closer to their ultimate commercialization.

## Conflict of interest statement. None declared.

Tong Yang<sup>1</sup> and Ming Yang<sup>1,2,\*</sup>

<sup>1</sup>Department of Applied Physics, The Hong Kong Polytechnic University, China and <sup>2</sup>Research Centre for Nanoscience and Nanotechnology,

The Hong Kong Polytechnic University, China \*Corresponding author.

E-mail: kevin.m.yang@polyu.edu.hk

## REFERENCES

- Lundstrom MS and Alam MA. Science 2022; 378: 722–3.

- 2. Schwierz F. Nat Nanotechnol 2010; 5: 487-96.

- 3. Kim S, Konar A, Hwang W-S *et al. Nat Commun* 2012: **3**: 1011.

- Wang X, Sun G, Routh P et al. Chem Soc Rev 2014;

43: 7067–98.

- 5. Zhou L, Liao L, Wang J *et al. Adv Mater* 2016; **28**: 2148–54.

- Liao L, Bai J, Cheng R et al. Nano Lett 2010; 10: 1917–21.

- Lin F, Cao Z, Xiao F et al. Natl Sci Rev 2024; 10: nwad279.

- 8. Liu Y, Rodrigues JNB, Luo YZ *et al. Nat Nanotech-nol* 2018; **13**: 828–34.

- 9. Bresniker K, Dukes S, Garner M *et al.* New Jersey, USA: IEEE, 2022, 3–31.