# Examination of Square-Wave Modulated Voltage Dip Restorer and Its Harmonics Analysis

K. W. E. Cheng, Senior Member, IEEE, S. L. Ho, K. P. Wong, Fellow, IEEE, T. K. Cheung, and Y. L. Ho

Abstract—The application of the square-wave compensation concept to the design of voltage dip restorer is presented in this paper. Both single square wave and multipulse square wave are used in this analysis. Both methods have shown to have a fast dynamic response as compared to that with sinusoidal compensation. The multipulse square wave can also compensate for zero crossing and the resultant distortion is small. Experimental results are reported to confirm the proposed method.

*Index Terms*—Harmonic distortion, high-speed electronics, inverters, power quality.

#### I. INTRODUCTION

OLTAGE dip is one of the main concerns of power quality for industry and for the electrical system management in buildings. It is more important than the other forms of power quality issues such as harmonics and power factor. This is mainly because of the extensive use of electronic and digital devices in modern electrical distribution as these devices are very sensitive to voltage dips. In a manufacturing plant, it may cause a complete shutdown of machinery and the associated financial losses could be very high. For buildings, the sudden shutdown of an escalator may result in an accident. The shutdown of the other power supplies or the elevators may cause inconvenience to the public. Voltage dip is also the major cause of power equipment shutdown

Typical reasons for voltage dip are due to the switching of high current load, cable fault, lightning strike, and faults in either the distribution or the transmission networks. In some cases, due to the magnetic coupling or incorrect wiring, fault current from one network could be coupled to the adjacent network. Fault current flowing in finite impedances could also give rise to voltage dips in the distribution systems [1], [5].

Typical voltage dip is usually of the order of tens to hundreds of milliseconds, but the damage would be extended over a long period and the associated financial loss may be very high. Typical examples affected in industrial processes are those in printing, glassmaking, garment manufacturing, and electroplating. Many of the modern devices trip when the supply voltage is

Manuscript received July 18, 2005; revised December 20, 2005. This work was supported in part by the Research Office and in part by the Department of Electrical Engineering of the Hong Kong Polytechnic University under Project A-PE40. Paper no. TEC-00239-2005.

K. W. E. Cheng, S. L. H. Ho, and K. P. Wong are with the Department of Electrical Engineering, The Hong Kong Polytechnic University, Hong Kong (e-mail: eeecheng@polyu.edu.hk; eeslho@polyu.edu.hk; eekpwong@polyu.edu.hk).

T. K. Cheung and Y. L. Ho are with the Design Engineer at Digipower Technology Ltd., Hong Kong (e-mail: eetkcheu@polyu.edu.hk; eeylho@polyu.edu.hk).

Digital Object Identifier 10.1109/TEC.2006.877366

reduced by more than 15% of the nominal value. High-intensity discharge (HID) lamps are being used commonly in stadium, playground, and as public lighting but they could be extinguished easily due to voltage dip and these lamps are unable to be switched on again within 5 min.

Many transient problems may only result in the loss of less than one cycle of the main's frequency. Typical causes are switching transients of heavy load or capacitor banks, electrostatic discharge, and large inverter starting transient.

Dynamic voltage restorer (DVR) [3]–[6] is now commonly used to compensate for the voltage dip. It is basically an electronic circuit that detects the voltage dip and produces necessary voltage to compensate for it. The line voltage in the network is then protected and any voltage dip is restored within a very short time. The associated appliances and voltage-sensitive devices are protected from fault.

The configuration of a DVR is basically to rectify ac into dc and the energy is stored using capacitors. The dc voltage is inverted into the ac, which is programmed to produce a corresponding amount of compensating voltage to offset the dips. Usually a transformer is used for isolation and voltage stepping. A common problem of the DVR is the response time. The device should respond to the voltage dips within a cycle. However, in order to give a sinusoidal voltage output, the dc/dc conversion of the DVR is realized using pulse-width modulation and a lowpass filter is needed. The dynamic performance of the low-pass filter is, however, a main concern. It usually slows down the dynamic response. Some DVRs use pure square wave instead of the sine wave. For these devices, even though the response is quick, as square waves can be generated instantaneously, the associated harmonics are large.

Another concern is isolation. Because a dc/ac converter is connected in series with the line, isolation is needed and the response time of the transformer then becomes a concern as virtually all power transformers operate at the mains frequency, which is usually 50/60 Hz. The transformer size is also large and it inevitably increases the total size of the DVR. Moreover, the reliability of the conventional DVR has not been studied thoroughly in reported literatures.

The size, weight, and cost of DVR therefore warrant improvement [7]. Conventionally, because of the use of isolation transformer, the total size of the DVR is dominated by the transformer. The overall weight and cost are therefore not favorable. However, by using high frequency switching techniques, the size of the transformer can be reduced significantly.

This paper proposes to solve all the above shortcomings. High-frequency switching method [8]–[11] is one of the techniques that can be used to reduce the total size. A special

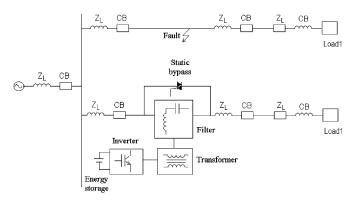

Fig. 1. Schematic of a classical DVR.

square-voltage excitation is proposed for the voltage dip compensation. A high-frequency transformer is used to replace the 50-/60-Hz transformer in order to improve the power density of the system [12], [13]. In this paper, the modulation method is introduced. The associated harmonic analysis is described so that the underlying reasons for the improvement in harmonics with the proposed voltage dip method can be understood thoroughly.

# II. CONVENTIONAL COMPENSATION METHOD FOR VOLTAGE DIP

The conventional method of voltage dip restorer is based on an inverter. Its voltage is regulated and added to the main's voltage in order to provide a fixed-voltage output. Fig. 1 shows a typical circuit of the DVR.  $Z_{\rm L}$  and CB are the line impedance and circuit breaker, respectively. When there is a fault in the adjacent line, the voltage dips and the DVR detects the dipped voltage. The inverter is then regulated to compensate for the differences in voltage. The output voltage is pulse-width modulation (PWM) regulated and therefore a low-pass filter is needed to change the PWM voltage into a sinusoidal ac. Because of the presence of the filter, the dynamic performance is slow when there is a voltage dip. An energy storage device is used to provide dc for the inverter during the voltage dip period. Usually the energy stored in the storage device is obtained from the mains through an ac/dc converter. A low-loss static switch, such as a triac or two thyristors connected in antiparallel, is used to bypass the mains current when there is no fault to ensure the normal current can pass through the line directly instead of via the DVR. Because of the isolation needed, a transformer is connected between the inverter and the line. This transformer operates at the mains frequency and therefore its size is large [14]. This conventional DVR is simulated with the condition of  $V_{\rm in} = 110$  V, voltage sag = 21 V, frequency = 50 Hz.

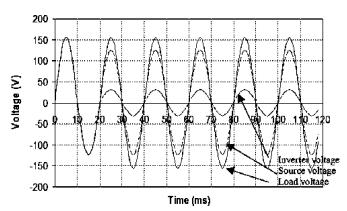

With a fault appearing at  $t=20\,$  ms, it can be seen from Fig. 2 that the line voltage takes several cycles before reaching the expected value.

### III. HIGH-FREQUENCY TRANSFOMER TECHNLOLOGY

#### A. High-Frequency Magnetics

The common 50-/60-Hz topology can be improved by using high-frequency power electronics. Firstly, the bulky isolation

Fig. 2. Voltages of the source, inverter, and load under a voltage sag with the compensation of a DVR using sinusoidal modulation

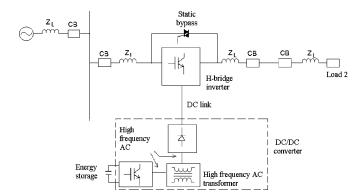

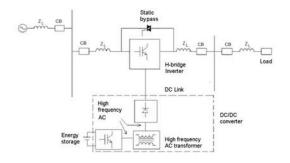

Fig. 3. High-frequency transformer used in a DVR.

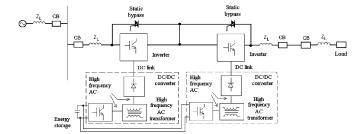

transformer operating at the mains frequency can be replaced by its high-frequency counterpart, which is physically much smaller. Fig. 3 shows the DVR using the high-frequency transformer. The high-frequency transformer proposed to be used in the isolated dc/dc converter can operate at several kilohertz or even at tens of kilohertz. Therefore, the transformer size can be reduced to as small as less than 1% of its mains counterpart. In addition to isolation, the transformer can serve to provide the necessary voltage conversion that is commonly required in the DVRs.

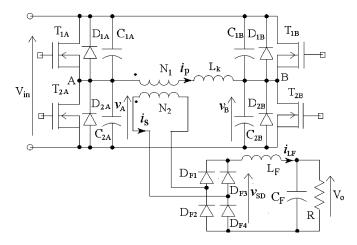

### B. DC-DC Converter

A high-frequency transformer requires a high-frequency dc/dc converter. For high-power application, a full-bridge phase-shifted converter is used because of the high power handling capability, soft switching of the power devices, and full utilization of the power transformer with such a configuration. Fig. 4 shows the converter circuit for use with the DVR. In the diagram,  $V_o$  is the output voltage of the dc–dc converter supplied to the inverter.  $V_{\rm in}$  is the input voltage for the converter and some energy storage components.  $D_{1A}$ ,  $D_{1B}$ ,  $D_{2A}$ , and  $D_{2B}$  are the antiparallel diodes of the main switching devices  $T_{1A}$ ,  $T_{1B}$ ,  $T_{2A}$ , and  $T_{2B}$ .  $C_{1A}$ ,  $C_{1B}$ ,  $C_{2A}$ , and  $C_{2B}$  are snubber capacitors to provide soft switching for the main switching devices. The high-frequency transformer windings have  $N_1$  and  $N_2$  turns for the primary and secondary windings, respectively.

Fig. 4. High-frequency dc-dc H-bridge converter.

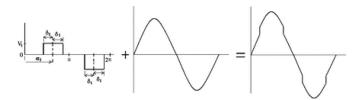

Fig. 5. Illustration of the square-wave compensation.

Fig. 6. DVR based on the sqaure wave.

# IV. SWITCHED-MODE COMPENSATION

Making use of the high switching speed of the dc-dc converter, the output stage of the converter serves to provide high dynamic responses. The waveform gives a compensated switched mode voltage for the DVR.

# A. Single Square Switching-Waveform Compensation

The compensation of the dipped voltage is assessed firstly using a switching waveform. Fig. 5 shows the effect of the voltage dip compensation based on a square wave with an amplitude of  $V_1$  and the pulse width is  $2\delta_1$ . The basic need for the DVR is to give the right voltage to the system, and the secondary need is to reduce the harmonic content. Fig. 6 shows the modification of the circuit with the inverter directly connected to the load bus. In the diagram, CB is the circuit breaker,  $Z_{\rm L}$  is the line impedance. Although the inverter output is not exactly sinusoidal, the harmonic could be confined within an acceptable

limit. Therefore, it is interesting to see the harmonic content of the proposed method and understand the corresponding variations as compared to those from a square wave.

The required voltage produced after the compensation  $V_{\rm com}$  is

$$V_{\text{com}} = V_s \sin \omega t + f(v) \tag{1}$$

where  $V_{\rm s}\sin\omega t$  is the mains voltage and f(v) is the compensating square-wave voltage from the DVR. The root mean square (rms) voltage of the compensated voltage is

$$V_{\text{com}}^2 = \frac{1}{2\pi} \int_0^{2\pi} (V_s \sin \omega t + f(v))^2 dt.$$

(2)

Because of the symmetry, the rms voltage  $V_{\text{comrms}}$  is

$$V_{\text{com}_{\text{rms}}}^2 = V_{s_{\text{rms}}}^2 + f(v)_{\text{rms}}^2 + \frac{4V_s V_1 \sin \delta_1}{2\pi}$$

(3)

where  $V_{\text{Srms}}$  and  $f(v)_{\text{rms}}$  are the rms voltages of  $V_s$  and f(v) respectively. The pulse width is limited by

$$0 \le \delta_1 \le \frac{\pi}{2}.\tag{4}$$

The harmonic contents of the compensation have been derived using the Fourier Series. The kth complex harmonic is

$$A_k = \frac{1}{2\pi} \int_0^{2\pi} f(v)e^{-jk\theta}d\theta \tag{5}$$

and

$$f(v) = \sum_{k=-\infty}^{\infty} A_k e^{jk\theta}.$$

(6)

It leads to

$$A_n = \frac{2V_1}{k\pi} j \sin k\delta_1 \sin \frac{k\pi}{2} e^{-jk\pi}.$$

(7)

It can be reduced to

$$|A_k| = \frac{2V_1}{k\pi} \sin k\delta_1 \quad k = \text{odd.}$$

(8)

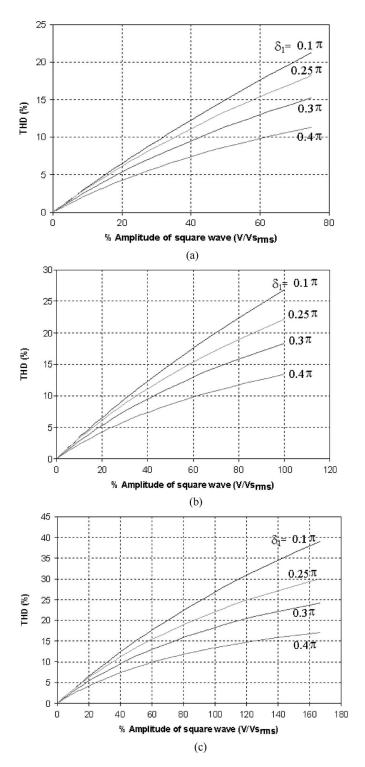

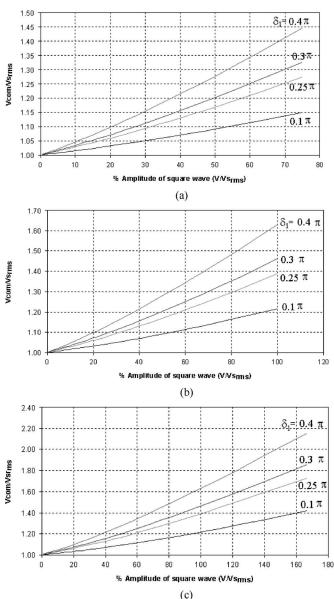

Fig. 7 shows the characteristics of the total harmonic distortion (THD) due to the square-wave compensation. All the voltages are normalized with respect to the base value of  $V_{\rm srms}$ . The characteristics for THD vary with  $V_s$  and  $V_{\rm Scom}$  for each case of 200, 150, and 90 V. In each case, a number of duty ratios were shown. It can be seen that as the source voltage increases, the THD decreases as expected. The lower the pulse width of the square wave, the higher the harmonic content.

The  $V_{\rm com}$  after the compensation is shown in Fig. 8. It indicates that the  $V_{\rm com}$  increases with increases in both the amplitude and the pulse width of the square wave. It gives a graphical design method to help the designers to select the square-wave compensation.

# B. Experimental Results

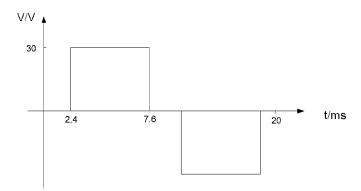

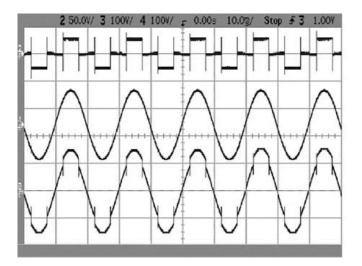

An H-bridge converter is used to generate the square waves for the compensation. The compensated voltage has an amplitude of 30 V and a pulse width of 5.1 ms. The test condition is based on the ac source voltage being sagged to 90  $V_{\rm rms}$ . Fig. 9 shows the compensating square wave generated by an H-bridge converter. Fig. 10 shows the experimental compensating square

Fig. 7. Total harmonics distortion versus the amplitude of square wave and pulse width.

wave, uncompensated sagged sinusoidal source voltage, and the compensated source voltage. It can be seen that the compensated voltage is not a pure sine wave but with lots of harmonics as expected. The rms voltage becomes 106 V.

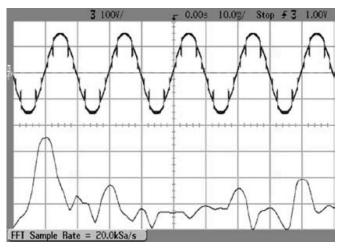

The Fourier analysis of the compensated waveforms is analyzed to check if the proposed method could give rise to serious deterioration in terms of harmonic distortion. Fig. 11 shows the fast Fourier transform (FFT) measurement. It can be seen that

Fig. 8. Compensated rms voltage after applying the DVR.

there are odd harmonics and the THD measured is 11.5%. The results agree with the theoretical prediction as shown in (2) and Fig. 7. The error is less than 20% for the THD and less than 5% for the rms voltage.

#### V. MULTIPLE SQUARE-WAVEFORM COMPENSATION

# A. Method of Multiple Waveform

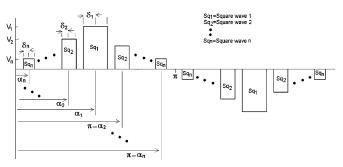

Although the above method gives rise to a small voltage distortion, it is possible to use multiple square waves to further reduce the harmonic content of the compensated waveform. Fig. 12 shows the schematic of the proposed multiple-waveform compensation.

The required voltage produced after the compensation  $V_{\rm com}$  is

$$V_{\text{com}} = V_s \sin \omega t + \sum_{i=1}^n f_i(v)$$

(9)

Fig. 9. Compensation voltage generated by the DVR.

Fig. 10. Experimental waveforms of the DVR. Top; Ch 2: compensation voltage of DVR (50 V/div); middle; Ch 4: source voltage (100 V/div); bottom; Ch 3: load voltage (100 V/div).

where  $f_i(v)$  are the square wave i. The rms voltage of the compensated voltage is

$$V_{\text{com}}^2 = \frac{1}{2\pi} \int_0^{2\pi} \left( V_s \sin \omega t + \sum_{i=1}^n f_i(v) \right)^2 dt.$$

(10)

Because of the symmetry, the rms voltage is

$$V_{\text{com}}^{2} = V_{s_{\text{rms}}}^{2} + \sum_{i=1}^{n} f_{i}(v)_{\text{rms}}^{2} + \frac{4V_{s}V_{1}\sin\delta_{1}}{2\pi} + \frac{8\sum_{i=2}^{n} V_{s}V_{i}\sin\alpha_{i}\sin\delta_{i}}{2\pi}.$$

(11)

The harmonic content of the above square waveforms can also be examined using the Fourier analysis. The phase angle of the positive pulse of the Square wave 1 is  $\alpha_1$ , its amplitude is  $V_1$ , and its pulse width is  $2\delta_1$ . The phase angle of the first positive pulse of the other square wave i is  $\alpha_i$ , its amplitude is  $V_i$  and its pulse width is  $2\delta_i$ . The limiting condition for the compensation is

$$0 \le \delta_1 + 2\sum_{i=2}^n \delta_i \le \frac{\pi}{2}.$$

(12)

Fig. 11. FFT of the load voltage after compensation. [Top: load voltage 100 V/div; bottom: FFT of load voltage vertical: 20 dB/div, horizontal: 50 Hz/div].

Fig. 12. Format of the multiple waveforms.

The amplitude of the kth complex harmonic is

$$A_{k} = \frac{V_{1}}{k\pi} \sin k\delta_{1} \left(e^{-jk\frac{\pi}{2}} - e^{-jk\frac{3\pi}{2}}\right) + \sum_{i=2}^{n} \frac{V_{i}}{k\pi} \sin k\delta_{i} \left(e^{-jk\alpha_{i}} - e^{-jk(\pi + \alpha_{i})} + e^{-jk(\pi - \alpha_{i})} - e^{-jk(2\pi - \alpha_{i})}\right).$$

(13)

It is reduced to

$$A_{k} = \frac{2V}{k\pi} j \sin k\delta \sin \frac{k\pi}{2} e^{-jk\pi}$$

$$+ \sum_{i=2}^{n} \frac{4V_{i}}{k\pi} j \sin k\delta_{i} \sin k\alpha_{i} \cos k\frac{\pi}{2} e^{-jk\frac{\pi}{2}}.$$

(14)

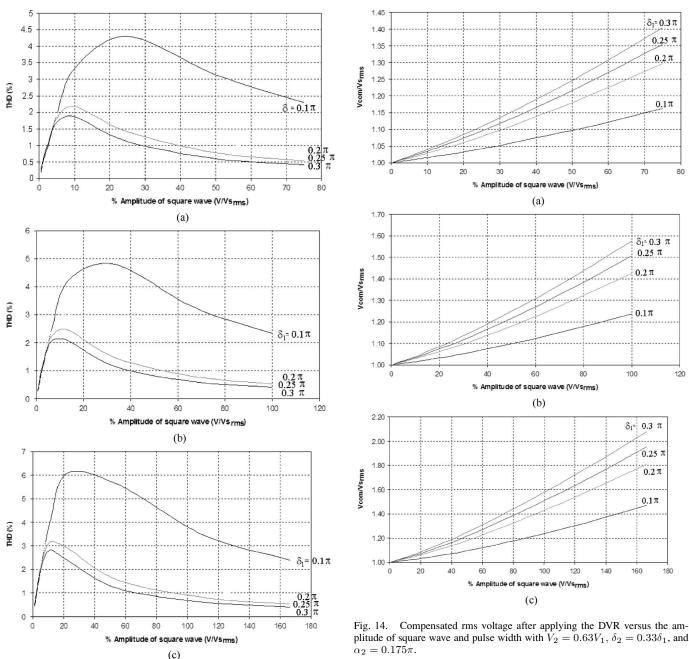

Fig. 13 shows the THD of the multipulse systems. It can be seen that the compensated waveform has a much lower THD as compared to that of the single-pulse version. Again, the curves are normalized with respect to the base of the source voltage  $V_{\rm srms}.$  In each curve, there is a maximum at a certain value of the applied square wave and, in general, the THD is less than 6% for most operations.

Fig. 14 shows the rms values of the compensated voltage. It can be used to find out the required amount of compensation. For both THD and  $V_{\text{com}}$ , they are quite independent of  $\alpha_2$ .

Fig. 13. Total harmonics distortion versus the amplitude of square wave and

pulse width with  $V_2 = 0.63V_1$ ,  $\delta_2 = 0.33\delta_1$ , and  $\alpha_2 = 0.175\pi$ .

# B. Applications to Mode 2 System

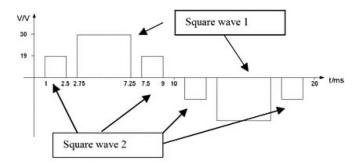

A Mode 2 system that is n=2 is examined in the exercise. Fig. 15 shows the schematic of the waveform used in the test. The compensated waveforms consist of six pulses in each source frequency period.

Fig. 16 shows the implementation circuit. Two converters are used to provide the dc voltage to the inverters. Both the dc-dc converters are connected with an energy storage device. It can also be seen that the bypass triac is also needed for each inverter. The bypass triac is to connect the mains to the output directly when no voltage sag is detected. In this case, the antiparallel

diode of the inverter bridge will not affect the output waveform of the inverter.

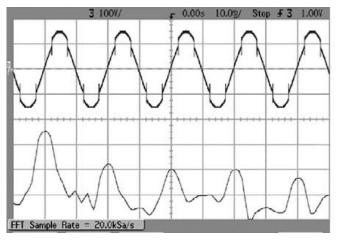

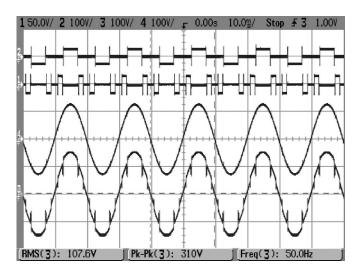

# C. Experimental Results

The dual quasi-square voltage is applied to the DVR. The aim of this part of the test is to see how the THD varies under the same compensated voltage  $V_{\rm com}$ . Fig. 17 shows the waveform for, from top to bottom waveforms, the square wave 1, square wave 2, dipped source voltage, and the load voltage. Square wave 1 is a simple bipolar quasi-square wave with a pulse value of 30 V and 4.5-ms pulse width. Square wave 2 is to provide a small amplitude square wave to compensate for the distortion near zero crossing. It consists of two pulses in each of the positive and negative cycles each has a magnitude of 19 V and a

Fig. 15. Dual waveform compensation.

Fig. 16. Electrical circuit for the multiple square-wave compensation.

Fig. 17. Waveforms of the dual square-wave method. Ch 1, square wave 2 (50 V/div); Ch 2, square wave 1 (100 V/div); Ch 3, output waveform (100 V/div); Ch 4, source voltage (100 V/div).

pulse width of 1.5-ms pulse. Channel 4 shows the source voltage which is dipped to 90  $V_{\rm rms}$ .

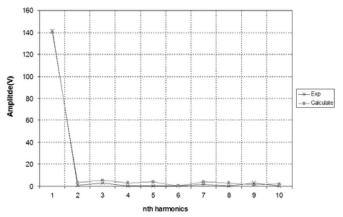

Fig. 18 shows the FFT for the load waveform. It can be seen that the harmonic distortion has been reduced by a large amount. The THD measured is 4%. It confirms that the proposed multipulse square-wave method can reduce the harmonics significantly. The voltage waveform is shown to have a very low percentage of harmonics.

Experimental results of the harmonics agree very well with the theoretical prediction as shown in (14). The direct comparison with the calculated harmonics is shown in Fig. 19. The overall harmonics of the proposed method is low and the method is simple for implementation.

Fig. 18. FFT of the load voltage after compensation using the dual square method. Top: load voltage 100 V/div; bottom: vertical: 20 dB/div, horizontal: 50 Hz/div.

Fig. 19. Comparison of the measured the calculated and measured harmonics.

# VI. DISCUSSION

From the above analysis, it can be seen that the dual square-wave method can provide a simple and improved compensation to the single square-wave compensation. No filter components are needed in the output stage of the inverter. Therefore, there is a reduction in the total size and cost. The dynamic response is very fast as the DVR does not need to handle low-frequency components. The load voltage also has a very low distortion.

Because sinusoidal pulse-width modulation is used in a classical inverter, a large LC filter is needed. Consequently, the total size of the DVR hinges largely on the size of the LC filter. The response of the LC filter also takes a few cycles before it settles down to steady state.

The proposed method uses a dc–dc converter with a high-frequency transformer as the isolation. The size of the transformer as well as the system can be reduced as a result. If a 50-Hz transformer is used and is connected to the inverter's output side, the transformer size and the system size will be dictated by the 50-Hz design and the overall size of such DVRs is not favourable when compared to the proposed design.

# VII. CONCLUSION

Square-wave compensation for use in the DVR is studied. Two methods have been proposed. One is the single square-wave method and the other is a dual square-wave method. The corresponding circuit is simple. For both methods, a high-frequency dc–dc converter is used to provide the required dc voltage to the square-wave generation. Because no 50-Hz compensation is needed and a high-frequency transformer is used, the DVR components have a high power density. The LC filter is no longer needed. The experimental waveform shows that the dual square wave has promising results for the optimal design of the DVR.

#### REFERENCES

- I. Hunter, "Power quality issues—a distribution company perspective," *Power Eng. J.*, vol. 15, no. 2, pp. 75–80, Apr. 2001.

- [2] T. Ino, T. Shindo, H. Motoyama, I. Kurihara, and K. Yoshimura, "Instantaneous voltage dip hazard map on power system," in *Proc. IEEE/PES Transmiss. Distrib. Conf. Exhib.*, Oct. 2002, Asia Pacific, pp. 1050–1053.

- [3] S. Quaia and F. Tosato, "A method for the computation of the interruption costs caused by supply voltage dips and outages in small industrial plants," in *Proc. IEEE EUROCON*, Sep. 22–24, 2003, vol. 2, pp. 249–253.

- [4] C. W. Toh, C. S. Lock, S. Chen, and S. S. Choi, "A voltage quality improvement solution using step dynamic voltage regulator," in *Proc Int. Conf. Power Syst. Technol.* Dec. 4–7, 2000, vol. 2, pp. 983–988.

- [5] H. Foch, P. Michalak, H. Pouliquen, and R. Tounsi, "Control laws for a voltage dip series compensator," in *Inst. Electr. Eng.-Proc. Power Elec*tron. Variable Speed Drives, 2000, pp. 21–23.

- [6] D. Armhof, P. Dahler, H. Gruning, and A. Kara, "Power supply quality improvement with a dynamic voltage restorer," in *Proc. IEEE APEC*, 1998, vol. 2, pp. 986–993.

- [7] Y. Kataoka, K. Matsushita, and M. Ono, "High speed switchgear protecting power generating facilities against voltage dip and interruption," in *Proc. IEEE Power Electron. Drive Syst. Conf.*, 1995, vol. 2, pp. 726–731.

- [8] K. W. E. Cheng and P. D. Evans, "The unified theory of extended-period quasi-resonant converter," in *Inst. Electr. Eng.-Proc. Electr. Power Appl.*, Mar. 2000, vol. 147, no. 2, pp. 127–132.

- [9] K. W. E Cheng, "Zero-voltage-switching modulation technique for resonant pole inverter," *Electron. Lett.*, vol. 35, no. 9, pp. 692–693, Apr. 1999

- [10] Y. P. Yeung, K. W. E. Cheng, D. Sutanto, and S. L. Ho, "Zero-current switching switched-capacitor quasi-resonant step-down converter," in *Inst. Electr. Eng.-Proc. Electr. Power Appl.*, Mar. 2002, vol. 149, no. 2, pp. 111–121.

- [11] Y. P. B. Yeung, K. W. E Cheng, S. L. Ho, and D. Sutanto, "Generalised analysis of switched-capacitor step-down quasi-resonant converter," *Electron. Lett.*, vol. 38, no. 6, pp. 263–264, Mar. 2002.

- [12] K. W. E. Cheng, "Computation of the ac resistance of multistranded conductor inductors with multilayers for high-frequency switching converters," *IEEE Trans. Magn.*, vol. 36, no. 4, pp. 831–834, Jul. 2000.

- [13] K. W. E. Cheng, "Modeling of solenoidal transformer for the calculation of leakage inductance using eddy current reaction field," *IEEE Trans. Magn.*, vol. 41, no. 5, pp. 1996–1999, May 2005.

- [14] C. Fitzer, M. Barnes, and P. Green, "Voltage sag detection techniques for a dynamic voltage restorer," *IEEE Trans. Ind. Appl.*, vol. 40, no. 1, pp. 203–212, Jan. 2004.

**K. W. E. Cheng** (M'90–SM'06) received the B.Sc. and Ph.D. degrees both from the University of Bath, Bath, U.K. in 1987 and 1990, respectively.

Before he joined the Hong Kong Polytechnic University, Hong Kong in 1997, he was with Lucas Aerospace, Birmingham, U.K. as a Principal Engineer and led a number of power electronics projects. He is now the Professor of the Department of Electrical Engineering and Director of the Power Electronics Research Center at the Hong Kong Polytechnic University, He has published over 200 papers and seven

books. His current research interests include all aspects of power electronics, motor drives, electromagnetic interference, and energy saving.

Dr. Cheng received the Inst. Electr. Eng. Sebastian Z De Ferranti Premium Award (1995), the Outstanding Consultancy Award (2000), the Faculty Merit Award for Best Teaching (2003) and Research & Scholarly Activities (2006) Award from the Hong Kong Polytechnic University, and Notable Mention of the Hong Kong Eco-Products Award (2006).

**S. L. Ho** received the B.Sc. and Ph.D. degrees in electrical engineering from the University of Warwick, Coventry, U.K., in 1976 and 1979, respectively.

He joined the then Hong Kong Polytechnic, Hong Kong in 1979 and is now a Chair Professor in Electrical Utilisation in the Department of Electrical Engineering, Hong Kong Polytechnic University, Hong Kong. Since joining the university, he has been working actively with local industry, particularly in railway engineering. He is the holder of several patents and has published over 100 papers in leading jour-

nals, mostly in the IEEE TRANSACTIONS and *Institution of Electrical Engineers Proceedings*. His current research interests include traction engineering, the application of finite elements in electrical machines, phantom loading of machines, and optimization of electromagnetic devices.

Dr. Ho is a member of the Institution of Electrical Engineers, U.K. and the Hong Kong Institution of Engineers.

**K. P. Wong** (M'87–SM'90–F'02) received the M.Sc., Ph.D. and D.Eng. degrees from the University of Manchester, Institute of Science and Technology (UMIST), Manchester, U.K. in 1972, 1974, and 2001, respectively.

He is currently a Chair Professor and is the Head of the Department of Electrical Engineering, The Hong Kong Polytechnic University, Hong Kong. He has published numerous research papers in power systems and in the applications of artificial intelligence and evolutionary computation to power system plan-

ning and operations. His current research interests include evolutionary optimization in power, power market analysis, power system planning and operation in deregulated environment, and power quality.

Prof. Wong received three Sir John Madsen Medals (1981, 1982, and 1988) from the Institute of Engineers Australia, the 1999 Outstanding Engineer Award from the IEEE Power Chapter Western Australia, and the 2000 IEEE Third Millennium Award. He is a Fellow of the Institution of Electrical Engineers, U.K. HKIE, and the IEAust.

T. K. Cheung started his research in power electronics in 2000 at the Hong Kong Polytechnic University, Hong Kong. He received the B.Eng. in 2004 from the same university.

He is currently the Design Engineer at Digipower Technology Ltd., Hong Kong. His current research interests include power converter controller design.

Y. L. Ho started his research in power electronics in 2000 at the Hong Kong Polytechnic University, Hong Kong, where he received the B.Eng. in 2004.

He is currently the Design Engineer at Digipower Technology Ltd., Hong Kong. His current research interests include static power converter design.