## Solution-processed p-type copper(I) thiocyanate (CuSCN) for low-voltage flexible thin-film transistors and integrated inverter circuits

Cite as: Appl. Phys. Lett. 110, 113504 (2017); https://doi.org/10.1063/1.4978531 Submitted: 24 November 2016 . Accepted: 01 March 2017 . Published Online: 17 March 2017

Luisa Petti, Pichaya Pattanasattayavong [10], Yen-Hung Lin, Niko Münzenrieder [10], Giuseppe Cantarella, Nir Yaacobi-Gross, Feng Yan, Gerhard Tröster, and Thomas D. Anthopoulos [10]

## ARTICLES YOU MAY BE INTERESTED IN

Metal oxide semiconductor thin-film transistors for flexible electronics Applied Physics Reviews 3, 021303 (2016); https://doi.org/10.1063/1.4953034

Copper thiocyanate: An attractive hole transport/extraction layer for use in organic photovoltaic cells

Applied Physics Letters 107, 013301 (2015); https://doi.org/10.1063/1.4926408

Hole mobility modulation of solution-processed nickel oxide thin-film transistor based on high-k dielectric

Applied Physics Letters 108, 233506 (2016); https://doi.org/10.1063/1.4953460

## Solution-processed p-type copper(I) thiocyanate (CuSCN) for low-voltage flexible thin-film transistors and integrated inverter circuits

Luisa Petti, <sup>1,2</sup> Pichaya Pattanasattayavong, <sup>3</sup> Yen-Hung Lin, <sup>1</sup> Niko Münzenrieder, <sup>2,4</sup> Giuseppe Cantarella, <sup>2</sup> Nir Yaacobi-Gross, <sup>1</sup> Feng Yan, <sup>5</sup> Gerhard Tröster, <sup>2</sup> and Thomas D. Anthopoulos 1,6,a)

<sup>1</sup>Department of Physics and Centre for Plastic Electronics, Blackett Laboratory, Imperial College London, London SW7 2AZ, United Kingdom

<sup>2</sup>Electronics Laboratory, Swiss Federal Institute of Technology Zurich, Gloriastrasse 35, 8092 Zurich, Switzerland

$^{3}$ Department of Materials Science and Engineering, School of Molecular Science and Engineering,

Vidyasirimedhi Institute of Science and Technology (VISTEC), Rayong 21210, Thailand

$^4$ Sensor Technology Research Center, School of Engineering and Informatics, University of Sussex, Falmer, Brighton BN1 9RH, United Kingdom

<sup>5</sup>Department of Applied Physics and Materials Research Centre, The Hong Kong Polytechnic University, Hong Kong, China

<sup>6</sup>Materials Science and Engineering, Division of Physical Sciences and Engineering, King Abdullah University of Science and Technology, Thuwal 23955-6900, Saudi Arabia

(Received 24 November 2016; accepted 1 March 2017; published online 17 March 2017)

We report on low operating voltage thin-film transistors (TFTs) and integrated inverters based on copper(I) thiocyanate (CuSCN) layers processed from solution at low temperature on freestanding plastic foils. As-fabricated coplanar bottom-gate and staggered top-gate TFTs exhibit hole-transporting characteristics with average mobility values of 0.0016 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $0.013 \,\mathrm{cm^2 \, V^{-1} \, s^{-1}}$ , respectively, current on/off ratio in the range  $10^2 - 10^4$ , and maximum operating voltages between -3.5 and -10 V, depending on the gate dielectric employed. The promising TFT characteristics enable fabrication of unipolar NOT gates on flexible free-standing plastic substrates with voltage gain of 3.4 at voltages as low as -3.5 V. Importantly, discrete CuSCN transistors and integrated logic inverters remain fully functional even when mechanically bent to a tensile radius of 4 mm, demonstrating the potential of the technology for flexible electronics. Published by AIP Publishing. [http://dx.doi.org/10.1063/1.4978531]

Flexible thin-film transistors (TFTs) hold great potential for numerous emerging applications, including flexible and paper-like displays, wearable and textile integrated systems,<sup>2,3</sup> smart labels and intelligent packaging,<sup>2,4</sup> epidermal devices,<sup>5</sup> electronic skins,<sup>6</sup> as well as imperceptible, biomimetic, and transient implants.<sup>7–9</sup> In recent years tremendous advances have been achieved through the use of metal oxide semiconductors as the channel materials 10 as they combine processing versatility<sup>11</sup> and high electron carrier mobility<sup>12</sup> leading to realization of numerous functional systems including large-area digital<sup>13–15</sup> and analog<sup>15–17</sup> circuits composed of hundreds of TFTs. 13 Despite the impressive progress, however, further developments are hampered by the lack of p-type semiconductors with performance and stability comparable to those found in their n-type counterparts. 18 So far only a handful of research groups have reported flexible p-type TFTs based on either  $SnO_x^{18-22}$  or  $CuO_x^{23-25}$  metal oxide semiconductors. Even though a hole mobility value up to  $5.87 \,\mathrm{cm^2 \, V^{-1} \, s^{-1}}$  has been reported, <sup>20</sup> the vacuumdeposition techniques (e.g., DC<sup>19,20,24</sup> or RF<sup>21–23</sup> sputtering) often used rely on relatively high annealing temperatures >150 °C, which in turn render the technologies incompatible with inexpensive plastic substrates. As a result, to date there is a continuous quest for alternative p-type materials that can

be grown at low temperatures from solution-phase. 10 One such semiconductor is the copper(I) thiocyanate (CuSCN) an inorganic molecular compound—that exhibits intrinsic p-type conductivity, excellent transparency in the visible range due to its large optical band gap, and low-temperature solution-processability. 11,26,27 Recently, Pattanasattavavong et al. have reported the fabrication of TFTs and unipolar inverters based on solution-processed layers of CuSCN at temperatures as low as 80 °C. Resulting TFTs and circuits showed excellent p-channel operation with hole mobility values in the range of  $0.01-0.1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and signal gains of up to 2.<sup>26,27</sup> In spite of the low processing temperature, the presented devices have been fabricated on rigid or substrates.

Here, we report the development of flexible low-voltage CuSCN TFTs and logic integrated inverters processed from solution at extremely low temperatures of ≤80 °C. Discrete bottom-gate bottom-contact and top-gate bottom-contact CuSCN transistors fabricated on freestanding plastic foils exhibit unipolar p-channel behaviour with hole mobility values of  $0.0016 \,\mathrm{cm^2~V^{-1}~s^{-1}}$  and  $0.013 \,\mathrm{cm^2~V^{-1}~s^{-1}}$ , respectively. The characteristically reliable device operation allows realization of integrated unipolar voltage inverters (NOT gates) with both active and passive loads yielding input signal gains of up to 3.4 at a supply voltage down to  $-3.5 \,\mathrm{V}$ . Importantly, both discrete devices and integrated inverters remain fully operational even under tensile bending radii

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: t.anthopoulos@imperial.ac.uk

down to 4 mm, clearly demonstrating the potential of CuSCN as a p-channel semiconductor for the emerging field of flexible transparent electronics.

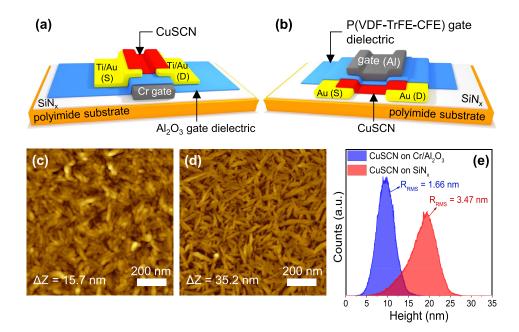

Coplanar bottom-gate bottom-contact (BG-BC) transistors were fabricated on a free-standing flexible polyimide (PI) foil (surface area of  $7.6 \times 7.6 \,\mathrm{cm}^2$ ). The 50  $\mu$ m-thick Kapton PI was chosen because of its low thermal  $(12 \times 10^{-6})$  $K^{-1}$ ) and humidity  $(9 \times 10^{-6} \% RH^{-1})$  expansion coefficients, its high glass transition temperature ( $T_g \sim 360\,^{\circ}\text{C}$ ), as well as its relatively low surface roughness (rms  $\sim 4$  nm).<sup>28</sup> Figure 1(a) shows the schematic device cross-section of the flexible BG-BC CuSCN TFTs. To provide a sufficient adhesion of the device layers to the flexible foil, 50 nm-thick layers of SiN<sub>X</sub> were grown on both sides of the PI substrate using plasma-enhanced chemical vapor deposition (PECVD). Next, a 30 nm layer of Cr was e-beam evaporated and patterned into bottom-gate contacts using standard UV photolithography and wet etching. Following, a 25 nm-thick Al<sub>2</sub>O<sub>3</sub> gate dielectric (dielectric constant  $\varepsilon_R = 9.5$ ) was grown by atomic layer deposition (ALD) at 150 °C. Gate contact holes through the dielectric were structured by photolithographic wet etching.<sup>25</sup> Subsequently, source and drain (S/D) contacts consisting of 10 nm/50 nm of Ti/Au were e-beam evaporated using lift-off. Prior to the semiconductor growth, the substrate was diced into chips of  $1.5 \times 1.5 \,\mathrm{cm}^2$ . The diced chips were sequentially cleaned by ultra-sonication in acetone and isopropanol baths for 5 min and subjected to UV/ozone treatment for 30 min. The active layer solution was prepared by dissolving the CuSCN precursor (Aldrich) in dipropyl sulfide (Merck, 99%) at a concentration of 20 mg ml<sup>-1</sup>. Undissolved material was removed by centrifuging and filtering the CuSCN solution at room temperature.<sup>26</sup> The solution was then spin-coated and annealed at 80 °C for 15 min under nitrogen atmosphere, yielding a 15 nmthick CuSCN layer. The resulting BG-BC TFTs had a channel length (L) and width (W) of 20  $\mu$ m and 1400  $\mu$ m, respectively.

In order to investigate the charge transport characteristics of as-deposited CuSCN layers as well as their compatibility with solution-processed gate dielectrics for flexible transistor applications, we incorporated CuSCN films into the

TG-BC TFT architecture [Figure 1(b)] and spin-coated the polymer dielectric. The CuSCN active layer was grown using the same process described above, whereas Au S/D and Al gate contacts were formed by thermal evaporation in high vacuum (10<sup>-6</sup> mbar) through shadow masks. As gate dielectric, poly(vinylidene fluoride-trifluoroethylene-chlorofluoroethylene) [P(VDF-TrFE-CFE)] layers were utilized. P(VDF-TrFE-CFE) is a high-k relaxor ferroelectric polymeric dielectric  $(\varepsilon_R \text{ up to } \approx 60)$ , which can be solution-processed at low temperatures.<sup>26,29</sup> The P(VDF-TrFE-CFE) with composition of 56/36.5/7.5 mol% was dissolved in methyl-ethyl-ketone (MEK) at a concentration of  $30 \,\mathrm{mg} \,\mathrm{ml}^{-1}$ . P(VDF-TrFE-CFE) films were spin-coated and subsequently annealed at  $60\,^{\circ}\text{C}$  for 3 h in nitrogen, resulting in a  $\sim$ 160 nm-thick layer. The channel dimensions of the resulting TG-BC TFTs were  $L = 40 \,\mu m$  and  $W = 1500 \,\mu m$ .

The surface morphology of the as-spun CuSCN films was studied by atomic force microscopy (AFM) in tapping mode. Figures 1(c) and 1(d) display the topographic images of CuSCN layers coated on PI/SiN<sub>x</sub>/Cr/Al<sub>2</sub>O<sub>3</sub> (for the BG-BC structure) and PI/SiN<sub>x</sub> (for the TG-BC structure), respectively, while Figure 1(e) shows the height distributions of the two layers. The CuSCN layer on Al<sub>2</sub>O<sub>3</sub> exhibits the common feature of elliptic domains, which have been previously reported for CuSCN films on glass, and also has a similar surface roughness (r.m.s value of  $\sim$ 1.7 nm). <sup>26,30</sup> The CuSCN domains for the layer deposited on SiN<sub>x</sub> appear longer and thinner, almost whisker-like, and the roughness increases slightly to 3.5 nm. The effects of the underlying layers and deposition conditions on the morphology of CuSCN films are still unclear and will be subject to further investigation. However, previous and current results show that the fieldeffect mobilities in CuSCN-based transistors fabricated on different substrates or from different solvents<sup>26,27,31,32</sup> are comparable to the values reported here. Although those CuSCN layers exhibited slightly different morphologies in terms of grain shape and size, their dimensions were in the same order of magnitude (10–100 nm). The nanocrystallinity and the associated high density of grain boundaries most

FIG. 1. Schematic cross-section of the (a) coplanar bottom-gate bottom-contact (BG-BC) and (b) staggered topgate bottom-contact (TG-BC) copper(I) thiocyanate (CuSCN) TFTs fabricated on free-standing polyimide substrates. AFM topography images of CuSCN films spin-coated onto (c) a polyimide/ SiN<sub>X</sub>/Cr/Al<sub>2</sub>O<sub>3</sub> and (d) a polyimide/ SiN<sub>X</sub> surface with the corresponding height distributions shown in (e).

likely play an important role at limiting the hole transport. Further work would be required to elucidate the exact nature of the charge transport and its dependence on the layer morphology/microstructure.

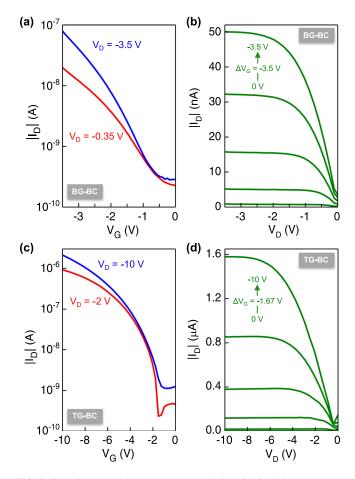

The charge transport properties of the as-deposited CuSCN films were investigated using the flexible BG-BC and TG-BC TFT architectures in dry nitrogen. Figure 2 displays a representative set of the transfer (a) and the output (b) characteristics measured for a representative flexible BG-BC CuSCN TFT. The device exhibits low voltage operation ( $\geq -3.5 \,\mathrm{V}$ ) and excellent hole transporting (p-channel) characteristics. Analysis of the transfer characteristics yields a current on/off ratio  $(I_{ON}/I_{OFF})$  of  $>10^2$ , a threshold voltage  $(V_{TH})$  of -1.5 V, a sub-threshold swing (SS) of  $\sim 1.7 \text{ V/dec}$ , and a saturation field-effect hole mobility ( $\mu_{SAT}$ ) of 0.0016 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The gate leakage (I<sub>G</sub>) remained always < 10 nA and as such did not interfere with the device operation. Analysis of the electrical characterization of 6 different TFTs across several different substrates yielded  $\mu_{SAT}$  and  $V_{TH}$  of 1.5  $(\pm 0.4) \times 10^{-3}$  cm<sup>2</sup>  $V^{-1}$  s<sup>-1</sup>and -1.5 ( $\pm 0.1$ ) V, respectively, showcasing the good uniformity of the fabrication process employed. Upon exposure to ambient air at room temperature (RH  $\sim 55\%$ ) for 30 min, the CuSCN TFTs remained fully functional and showed a 45% reduction in the effective mobility and a threshold voltage shift of approximately  $-400\,\mathrm{mV}$ . Importantly, the initial transistor characteristic is fully recovered when the

FIG. 2. Transfer (a) and output (b) characteristics of a flexible low-voltage BG-BC CuSCN p-type TFT with  $Al_2O_3$  gate dielectric (W = 1400  $\mu m$  and L = 20  $\mu m$ ). Transfer (c) and output (d) characteristics of a flexible low-voltage TG-BC CuSCN p-type TFT with P(VDF-TrFE-CFE) gate dielectric (W = 1500  $\mu m$  and L = 40  $\mu m$ ).

devices are re-exposed to nitrogen air, suggesting that no chemical changes are taking place within the CuSCN layer and that the observed effect is most likely due to physisorption of atmospheric oxidants, e.g., water and oxygen.

Nevertheless, the mobility values obtained here are generally lower than the average  $\mu_{\rm SAT}$  of 0.01–0.1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> reported previously for TG-BC CuSCN TFTs fabricated on rigid substrates. This is most likely attributed to the unfavorable coplanar BG-BC architecture, combined with the potentially higher concentration of trap states at the Al<sub>2</sub>O<sub>3</sub>/CuSCN interface. When similar CuSCN films were incorporated in an optimized staggered TG-BC flexible TFT geometry employing a high-k P(VDF-TrFE-CFE) gate dielectric [Figure 2(c)], the hole saturation mobility and the on/off current ratio reach higher values up to 0.013 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 2 × 10<sup>3</sup>, respectively. As shown in Figures 2(c) and 2(d), flexible TG-BC CuSCN TFTs exhibit clear p-type characteristics, with low-voltage operation and clear channel current saturation.

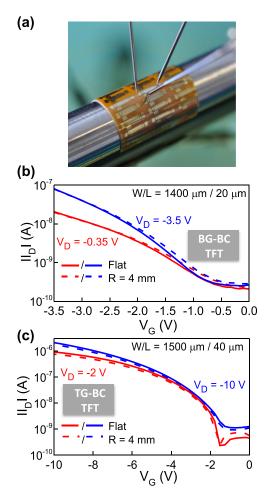

In addition to the electrical performance, the mechanical bendability of any emerging TFT technology is expected to play a key role in its widespread application. In order to test the mechanical properties of the CuSCN TFTs, we attached the flexible substrates to a double-sided adhesive tape and wound them around a metallic cylinder rod of 4 mm radius [Figure 3(a)], so that tensile strain was applied parallel to the transistor channel. Figures 3(b) and 3(c) display representative sets of transfer characteristics measured for a flexible BG-TB (b) and a TG-BC (c) CuSCN TFTs while flat (solid lines) and bent (dashed lines) to a tensile radius (R) of 4 mm. Evidently, both types of CuSCN TFTs remain fully operational even when bent to 4 mm radius (which corresponds to a strain  $\varepsilon \sim 0.58\%$  calculated using the approximation given by Gleskova et al.<sup>34</sup>) and show only minor and reversible changes in their performance characteristics. In particular, under tensile strain both BG-BC and TG-BC CuSCN TFTs exhibit a small reduction in  $\mu_{SAT}$  (down to 0.0013 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 0.01 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, respectively) and a slight positive shift ( $\sim$ 70 mV) in V<sub>TH</sub>. The use of a low gate-source voltage together with a 5-min interval between the TFT characterization while flat and while bent allows minimizing the influence of electric stress. The slightly reduced  $\mu_{\mathrm{SAT}}$  and the positively shifted V<sub>TH</sub> could possibly be attributed to the formation of micro-cracks within the nanocrystalline CuSCN layer. Compared with previously reported bending experiments of TFTs based on polycrystalline In<sub>2</sub>O<sub>3</sub><sup>35</sup> and nanocrystalline ZnO, 35,36 our CuSCN devices result in the same trend with 83% smaller variations at comparably low bending radii. Specifically, In<sub>2</sub>O<sub>3</sub>- and ZnO-based devices exhibit 98% to 99% reduction in  $\mu_{SAT}$  and 1.2 V to 1V shift in  $V_{TH}$ while bent to 10 mm radii whereas our CuSCN TFTs only show 16%  $\mu_{SAT}$  reduction and 70 mV V<sub>TH</sub> shift at 4 mm. Also, re-flattening of the devices allows closing up the microcracks and therefore leads to a full recovery of the un-strained TFT performance. Nevertheless, bending to even smaller radii induces cracks that permanently harm the device operation. These results demonstrate the superior mechanical stability of our p-type crystalline CuSCN TFTs and their suitability for application in large-area flexible electronics.

The promising CuSCN TFT characteristics prompted us to explore this interesting technology for application in

FIG. 3. (a) Photograph of a flexible CuSCN TFT mechanically bent to a tensile radius of 4 mm. Transfer characteristics of a BG-BC (b) and a TG-BC (c) CuSCN TFTs measured while flat (solid lines) and subsequently bent (dashed lines) to a tensile radius of 4 mm.

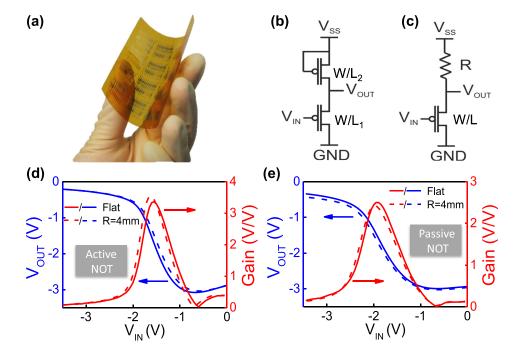

flexible integrated inverters. Figure 4(a) shows a photograph of an as-processed flexible substrate  $(7.6 \times 7.6 \text{ cm}^2 \text{ in size})$  containing various CuSCN-based NOT gates based on active [Figure 4(b)] and passive [Figure 4(c)] circuitry. Electrical

characterization of discrete CuSCN transistors was used to design logic inverters with centered midpoint voltages  $V_M \approx V_{SS}/2$ . Integrated inverters with active load consisted of a driving and a load CuSCN TFTs with W/L of  $3200~\mu\text{m}/20~\mu\text{m}$  and  $450~\mu\text{m}/20~\mu\text{m}$ , respectively, whereas the inverter with passive load combines a driving TFT with W/L =  $2100~\mu\text{m}/20~\mu\text{m}$  and a passive load resistor with resistance R =  $170~\text{k}\Omega$ . All the CuSCN TFTs were fabricated using the more practical BG-BC device architecture whereas the resistor used in the passive load inverter was implemented using the Cr gate metal itself (resistivity  $\rho = 1.16 \times 10^{-6}~\Omega$ ·m). All the interconnections were integrated into the Ti/Au S/D metallization layer, eliminating the need for additional processing steps.

Figure 4(d) shows the voltage transfer characteristic (VTC) and the corresponding signal gain (G) of the NOT gate in active configuration measured at a supply voltage V<sub>SS</sub> of -3.5 V. The inverter exhibits G = 3.4, an almost centered  $V_{\rm M}$ of  $-1.5 \,\mathrm{V}$ , and a good output swing (output high voltage  $V_{OH} = -0.2 \text{ V}$  and output low voltage  $V_{OL} = -2.9 \text{ V}$ ) even at a low  $V_{SS}$  of -3.5 V. Inverters with passive load [Figure 4(e)] based on flexible CuSCN TFTs and Cr resistor yield similar performance (G = 2.5 and  $V_M = -1.95 \, V$ ), demonstrating the high degree of flexibility of our technology as well as the reproducibility of the CuSCN TFTs. Furthermore, both NOT gates were fully functional while mechanically bent to 4 mm tensile radius [Figures 4(d) and 4(e)]. The small variations observed in the CuSCN inverter performance parameters (changes in G and  $V_M$  of  $\pm 4\%$  and  $\pm 100 \,\mathrm{mV}$ , respectively) are attributed to the strain-induced changes in the TFT/resistor performance. Additionally, inverters with passive loads remained operational after being exposed for 30 min to ambient air, demonstrating good stability towards atmospheric oxidants.

In summary, we have developed flexible p-channel TFTs and unipolar integrated NOT gate circuits based on CuSCN p-type semiconductor layers processed from solution-phase at 80 °C. The resulting CuSCN transistors exhibit low operating

FIG. 4. (a) Photograph of a fully processed flexible substrate comprising several CuSCN-based integrated circuits. Circuit schematics of a unipolar voltage inverter (NOT gate) in active (b) and passive (c) load configuration based on p-channel TFTs. Voltage transfer characteristics and corresponding signal gain curves for NOT gates based on active (d) and passive (e) circuitry employing CuSCN p-type TFTs, measured at a supply voltage  $(V_{SS})$  of  $-3.5\,V$  while flat (solid lines) and bent (dashed lines) to a tensile radius of 4 mm. The inverter in active configuration comprises a driving and a load CuSCN TFT with W/L of, respectively, 3200 µm/20 µm and  $450 \,\mu\text{m}/20 \,\mu\text{m}$ , whereas the NOT gate with passive load comprises a driving TFT with W/L =  $2100 \,\mu\text{m}/20 \,\mu\text{m}$  and a passive load  $170 \,\mathrm{k}\Omega$  resistor.

voltages with a maximum hole mobility of  $0.013\,\mathrm{cm^2~V^{-1}s^{-1}}$  and on/off channel current ratio of  $\sim 10^3$ . Different unipolar NOT gates made using a combination of CuSCN TFTs and load resistors exhibit excellent inverting characteristics with input signal gain up to 3.4 and operating voltages down to  $-3.5\,\mathrm{V}$ . Finally, CuSCN TFTs and inverter circuits were shown to remain fully functional even when mechanically bent to a tensile radius of 4 mm. This work further asserts CuSCN as a promising p-type transparent semiconductor for application in flexible, large-area electronics.

The authors would like to acknowledge N. Wijeyasinghe from Imperial College London for her support during the device and circuit fabrication and characterization.

- <sup>1</sup>P. Heremans, A. K. Tripathi, A. D. de Meux, E. C. P. Smits, B. Hou, G. Pourtois, and G. H. Gelinck, Adv. Mater. **28**(22), 4266–4282 (2016).

- <sup>2</sup>A. Nathan, A. Ahnood, M. T. Cole, S. Lee, Y. Suzuki, P. Hiralal, F. Bonaccorso, T. Hasan, L. Garcia-Gancedo, A. Dyadyusha, S. Haque, P. Andrew, S. Hofmann, J. Moultrie, D. P. Chu, A. J. Flewitt, A. C. Ferrari, M. J. Kelly, J. Robertson, G. A. J. Amaratunga, and W. I. Milne, Proc. IEEE 100, 1486–1517 (2012).

- K. Cherenack and L. van Pieterson, J. Appl. Phys. 112(9), 091301 (2012).

D. Makarov, M. Melzer, D. Karnaushenko, and O. G. Schmidt, Appl. Phys. Rev. 3(1), 011101 (2016).

- <sup>5</sup>T. Sekitani and T. Someya, MRS Bull. **37**(3), 236–245 (2012).

- <sup>6</sup>M. L. Hammock, A. Chortos, B. C. K. Tee, J. B. H. Tok, and Z. A. Bao, Adv. Mater. 25(42), 5997–6037 (2013).

- <sup>7</sup>G. Park, H. J. Chung, K. Kim, S. A. Lim, J. Kim, Y. S. Kim, Y. Liu, W. H. Yeo, R. H. Kim, S. S. Kim, J. S. Kim, Y. H. Jung, T. I. Kim, C. Yee, J. A. Rogers, and K. M. Lee, Adv. Healthcare Mater. 3(4), 515–525 (2014).

- <sup>8</sup>D. Karnaushenko, N. Munzenrieder, D. D. Karnaushenko, B. Koch, A. K. Meyer, S. Baunack, L. Petti, G. Troster, D. Makarov, and O. G. Schmidt, Adv. Mater. 27(43), 6797–6805 (2015).

- <sup>9</sup>S. Bauer, S. Bauer-Gogonea, I. Graz, M. Kaltenbrunner, C. Keplinger, and R. Schwodiauer, Adv. Mater. **26**(1), 149–162 (2014).

- <sup>10</sup>L. Petti, N. Munzenrieder, C. Vogt, H. Faber, L. Buthe, G. Cantarella, F. Bottacchi, T. D. Anthopoulos, and G. Troster, Appl. Phys. Rev. 3(2), 021303 (2016).

- <sup>11</sup>S. R. Thomas, P. Pattanasattayavong, and T. D. Anthopoulos, Chem. Soc. Rev. 42(16), 6910–6923 (2013).

- <sup>12</sup>Y. S. Rim, H. J. Chen, Y. S. Liu, S. H. Bae, H. J. Kim, and Y. Yang, ACS Nano 8(9), 9680–9686 (2014).

- <sup>13</sup>K. Myny and S. Steudel, ISSCC Dig. Tech. Pap. I **59**, 298–299 (2016).

- <sup>14</sup>A. K. Tripathi, E. C. P. Smits, J. B. P. H. van der Putten, M. van Neer, K. Myny, M. Nag, S. Steudel, P. Vicca, K. O'Neill, E. van Veenendaal, J. Genoe, P. Heremans, and G. H. Gelinck, Appl. Phys. Lett. 99(7), 079901 (2011).

- <sup>15</sup>G. Cantarella, K. Ishida, L. Petti, N. Munzenrieder, T. Meister, R. Shabanpour, C. Carta, F. Ellinger, G. Troster, and G. A. Salvatore, IEEE Electron Device Lett. 37, 1582–1585 (2016).

- <sup>16</sup>C. Zysset, N. Munzenrieder, L. Petti, L. Buthe, G. A. Salvatore, and G. Troster, IEEE Electron Device Lett. 34(11), 1394–1396 (2013).

- <sup>17</sup>K. Ishida, R. Shabanpour, B. K. Boroujeni, T. Meister, C. Carta, F. Ellinger, L. Petti, N. S. Munzenrieder, G. A. Salvatore, and G. Troster, in 2014 IEEE Asian Solid-State Circuits Conference (a-SSCC) (IEEE, 2014), pp. 313–316.

- pp. 313–316.

<sup>18</sup>Z. W. Wang, P. K. Nayak, J. A. Caraveo-Frescas, and H. N. Alshareef, Adv. Mater. 28(20), 3831–3892 (2016).

- <sup>19</sup>J. A. Caraveo-Frescas, M. A. Khan, and H. N. Alshareef, Sci. Rep. 4, 5243 (2014).

- <sup>20</sup>J. A. Caraveo-Frescas, P. K. Nayak, H. A. Al-Jawhari, D. B. Granato, U. Schwingenschlogl, and H. N. Alshareef, ACS Nano 7(6), 5160–5167 (2013).

- <sup>21</sup>R. F. P. Martins, A. Ahnood, N. Correia, L. M. N. P. Pereira, R. Barros, P. M. C. B. Barquinha, R. Costa, I. M. M. Ferreira, A. Nathan, and E. E. M. C. Fortunato, Adv. Funct. Mater. 23(17), 2153–2161 (2013).

- <sup>22</sup>R. Martins, A. Nathan, R. Barros, L. Pereira, P. Barquinha, N. Correia, R. Costa, A. Ahnood, I. Ferreira, and E. Fortunato, Adv. Mater. 23(39), 4491–4496 (2011).

- <sup>23</sup>A. Dindar, J. B. Kim, C. Fuentes-Hernandez, and B. Kippelen, Appl. Phys. Lett. **99**(17), 172104 (2011).

- <sup>24</sup>Z. Q. Yao, S. L. Liu, L. Zhang, B. He, A. Kumar, X. Jiang, W. J. Zhang, and G. Shao, Appl. Phys. Lett. **101**(4), 042114 (2012).

- <sup>25</sup>B. Zhou and W. F. Ramirez, J. Electrochem. Soc. **143**(2), 619–623 (1996).

- <sup>26</sup>P. Pattanasattayavong, N. Yaacobi-Gross, K. Zhao, G. O. N. Ndjawa, J. H. Li, F. Yan, B. C. O'Regan, A. Amassian, and T. D. Anthopoulos, Adv. Mater. 25(10), 1504–1509 (2013).

- <sup>27</sup>P. Pattanasattayavong, G. O. N. Ndjawa, K. Zhao, K. W. Chou, N. Yaacobi-Gross, B. C. O'Regan, A. Amassian, and T. D. Anthopoulos, Chem. Commun. 49(39), 4154–4156 (2013).

- <sup>28</sup>N. Munzenrieder, L. Petti, C. Zysset, T. Kinkeldei, G. A. Salvatore, and G. Troster, IEEE Trans. Electron Devices 60(9), 2815–2820 (2013).

- <sup>29</sup>J. H. Li, Z. H. Sun, and F. Yan, Adv. Mater. **24**(1), 88–93 (2012).

- <sup>30</sup>P. Pattanasattayavong, A. D. Mottram, F. Yan, and T. D. Anthopoulos, Adv. Funct. Mater. 25(43), 6802–6813 (2015).

- <sup>31</sup>P. Pattanasattayavong, Ph. D. thesis, Imperial College, London (2014).

- <sup>32</sup>N. Yaacobi-Gross, N. D. Treat, P. Pattanasattayavong, H. Faber, A. K. Perumal, N. Stingelin, D. D. Bradley, P. N. Stavrinou, M. Heeney, and T. D. Anthopoulos, Adv. Energy Mater. 5(3), 1401529 (2015).

- <sup>33</sup>C. H. Kim, Y. Bonnassieux, and G. Horowitz, IEEE Electron Device Lett. 32(9), 1302–1304 (2011).

- <sup>34</sup>H. Gleskova, S. Wagner, and Z. Suo, J. Non-Cryst. Solids **266**, 1320–1324 (2000).

- <sup>35</sup>X. G. Yu, L. Zeng, N. J. Zhou, P. J. Guo, F. Y. Shi, D. B. Buchholz, Q. Ma, J. S. Yu, V. P. Dravid, R. P. H. Chang, M. Bedzyk, T. J. Marks, and A. Facchetti, Adv. Mater. 27(14), 2390–2399 (2015).

- <sup>36</sup>K. H. Cherenack, N. S. Munzenrieder, and G. Troster, IEEE Electron Device Lett. **31**(11), 1254–1256 (2010).