# Synthesis of Input-Rectifierless AC/DC Converters

C. P. Liu, *Member, IEEE*, Chi K. Tse, *Senior Member, IEEE*, N. K. Poon, *Member, IEEE*, Bryan M. H. Pong, *Senior Member, IEEE*, and Y. M. Lai, *Member, IEEE*

Abstract—This paper discusses the basic construction procedure and topological possibilities of creating ac/dc converters out of simple dc/dc converters. It is shown that two separately controlled dc/dc converters are sufficient for producing a regulated dc output and shaping the input current, from an ac voltage source, without the need for input rectifiers. Some design constraints are discussed, emanating from the limitation of the conversion ratios that can be achieved by particular dc/dc converters. Selected topologies are verified experimentally. This kind of rectifierless converters find applications in airborne power supplies where zero-crossing distortions are significant because of the inevitable phase-lead effect of the input rectifier bridge.

Index Terms—AC/DC converter, circuit topology, control, dc/dc converter, rectifier.

### I. INTRODUCTION

C/DC converters without input rectifiers have received some attention because of their relative advantages in eliminating power loss in rectifiers and reducing harmonic distortions. In airborne applications where the mains frequency is as high as several hundreds hertz, the phase-lead effect of the input rectifier bridge in a power-factor-correction converter has been found to cause significant zero-crossing distortions which are impossible to eliminate [1]. Without input rectifiers, ac/dc converters would be free from zero-crossing distortions.

One straightforward approach to implement a rectifierless ac/dc converter is to construct two circuits (two complete converters), each working for either positive or negative half cycle of the line period. This approach, however, requires rather complicated circuits [2], [3]. Another possibility is to put the equivalent rectification in the secondary side where the diodes perform high-frequency as well as line-frequency rectification. This approach usually requires four quadrant switches and complicated topologies. Also, the high-current low-voltage condition in the secondary may present difficulty in raising the overall efficiency [4]. Recently, suitable converters having inherent ac/dc conversion capability have been studied by Ikriannikov and Ćuk [5]. However, such converters, known as *bipolar-gain* converters [5], do not seem to have a systematic origin from which general synthesis procedure can be derived.

Manuscript received January 27, 2003; revised July 15, 2003. This paper was presented in part at the IEEE Power Electronics Specialists Conference, Vancouver, Canada, 2001. Recommended by Associate Editor C. A. Canessin.

C. P. Liu, N. K. Poon, and B. M. H. Pong are with the Department of Electrical and Electronic Engineering, University of Hong Kong, Hong Kong (e-mail: cpliu@eee.hku.hk).

C. K. Tse and Y. M. Lai are with the Department of Electronic and Information Engineering, Hong Kong Polytechnic University, Kowloon, Hong Kong (e-mail: encktse@polyu.edu.hk).

Digital Object Identifier 10.1109/TPEL.2003.820577

In this paper we consider the *fundamental synthesis problem* of a converter that converts an unrectified ac voltage to a dc voltage, without using an input rectifier. Our aim is to derive the simplest topology for ac/dc conversion, based on a combination of dc/dc converters.

## II. DERIVATION OF THE SIMPLEST AC/DC CONVERTER

We begin with a black-box specification of ac/dc conversion. Let u(t) be the output voltage, and e(t) be the input voltage. The ac/dc conversion specifies that

$$\begin{cases} u(t) = U, & \text{where } U > 0 \\ e(t) = E \sin 2\pi f_e t, & \text{where } E > 0. \end{cases}$$

(1)

In other words, we consider the usual conversion of a sinusoidal input voltage having a peak of E and frequency  $f_e$  into a fixed output voltage U. Our purpose is to derive the simplest input-rectifierless topology based on dc/dc converters that can fulfil the above black-box requirement.

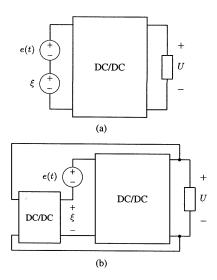

## A. Basic Construction

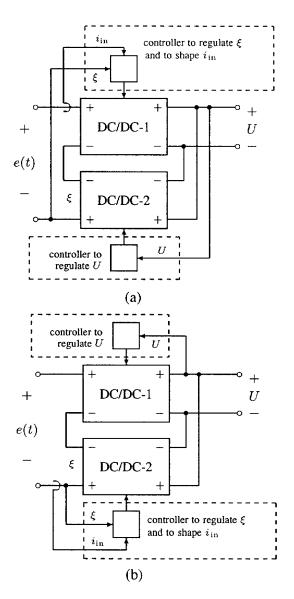

First of all, we observe that simple dc/dc converters only convert a dc voltage to another dc voltage. Thus, the use of a dc/dc converter for ac/dc conversion is handicapped mainly by its input side which cannot admit negative voltage values. The problem can be hypothetically solved if one stacks up a sufficiently large dc voltage over the ac input voltage before feeding into a dc/dc converter. This idea is illustrated in Fig. 1(a), where  $\xi$  denotes the stack-up voltage. Obviously, we need

$$\xi > E.$$

(2)

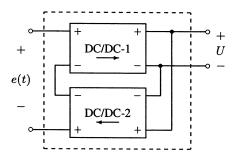

Our next logical step is to create the required  $\xi$ . Clearly we need a second dc/dc converter which choicelessly must convert from the output voltage U. This gives the basic configuration shown in Fig. 1(b), which is simply a series connection of two dc/dc converters. We may now construct our black-box ac/dc converter as shown in Fig. 2.

Remarks on isolation—It should be noted that when constructing the practical circuit, care should be taken to avoid short-circuit paths that may affect voltage conversion. One simple solution is to use isolated converters, though not always necessarily, to realize either converter 1 or converter 2. Moreover, if full isolation is required between e(t) and U, then both converters should be isolated.

## B. Constraints on Voltage Conversion Ratios

As shown in Fig. 2, converter 1 (labeled as DC/DC-1) must be capable of converting a variable dc voltage to a fixed dc voltage,

0885-8993/04\$20.00 © 2004 IEEE

Fig. 1. AC/DC conversion using (a) a dc/dc converter with a dc stack-up voltage and (b) two dc/dc converters.

Fig. 2. Simplest input-rectifierless ac/dc converter.

whereas converter 2 (labeled as DC/DC-2) converts a fixed dc voltage to another fixed dc voltage. Suppose the voltage conversion ratios of converter 1 and converter 2 are  $k_1$  and  $k_2$ , respectively. We have

$$U = k_1 \left[ e(t) + \xi \right] \tag{3}$$

$$\xi = k_2 U. \tag{4}$$

Combining the above equations, the overall conversion ratio is given by

$$\frac{U}{e(t)} = \frac{k_1}{1 - k_1 k_2}, \text{ for } e(t) \neq 0.$$

(5)

The case when e(t)=0 corresponds to zero-crossing of the input waveform, i.e.,  $t=n/2f_e$  where  $n=0,1,2,\ldots$  In this case, the input to converter 1 and the output from converter 2 are both equal to  $\xi$ , giving

$$k_1 = \frac{U}{\xi}$$

and  $k_1 k_2 = 1$ , for  $e(t) = 0$ . (6)

To determine the constraints on the choice of dc/dc converters, we first observe that

$$k_2 > \frac{E}{U} \tag{7}$$

because  $\xi > E$ . Thus, if E > U, then converter 2 must be a step-up converter; otherwise, it can be an either step-up or

step-down converter. Also, from (3), we can derive the range of  $k_1$  as

$$\frac{U}{\xi + E} < k_1 < \frac{U}{\xi - E}.\tag{8}$$

Thus, if  $U/(\xi+E)>1$ , converter 1 must be a step-up converter; if  $U/(\xi-E)<1$ , converter 1 must be a step-down converter; and if  $U/(\xi+E)<1$  and  $U/(\xi-E)>1$ , then converter 1 must be able to do both step-down and step-up at different time in a line cycle. Table III summarizes the choice of converters under different voltage conditions.

### C. Power Flow Consideration

We now consider the way in which power is processed in the basic configuration shown in Fig. 2. First of all, assuming that the input current has the form

$$i_{\rm in}(t) = \hat{i}_{\rm in} \sin 2\pi f_e t \tag{9}$$

the condition for power balance gives

$$\hat{i}_{\rm in} = \frac{2P_o}{E} \tag{10}$$

where  $P_o$  is the output power. Thus, the power processed by converter 1 (labeled as DC/DC-1),  $p_1(t)$ , is

$$p_1(t) = (E\sin 2\pi f_e t + \xi) i_{\rm in}(t)$$

(11)

and that by converter 2 (labeled as DC/DC-2),  $p_2(t)$ , is

$$p_2(t) = \xi i_{\rm in}(t). \tag{12}$$

Integrating over a half mains cycle, we get the power processed by converter 1 during the positive mains cycle and the negative half mains cycle, respectively, as

$$P_1^+ = 2f_e \int_0^{1/2f_e} (E\sin 2\pi f_e t + \xi) i_{\rm in}(t) dt = P_o \left( 1 + \frac{4\xi}{\pi E} \right)$$

(13)

and

$$P_{1}^{-} = 2f_{e} \int_{1/2f_{e}}^{1/f_{e}} (E \sin 2\pi f_{e} t + \xi) i_{\text{in}}(t) dt - P_{o} \left(\frac{4\xi}{\pi E}\right).$$

(14)

Likewise, we get the power processed by converter 2 during the positive mains cycle and the negative half mains cycle as

$$P_2^+ = -P_2^- = P_o\left(\frac{4\xi}{\pi E}\right). \tag{15}$$

Thus, we clearly see that the average power processed by converter 1 is  $P_o$  and that by converter 2 is zero, over one complete mains cycle. Both converters are required to be *bi-directional* since during the negative half mains cycle, power flow is essentially reversed. The overall effect is a circulation of power, which is equal to  $(4\xi/\pi E)$ , between the two converters. Such circulation may undesirably degrade the efficiency. Hence, to reduce this circulation, we may need to design the circuit with a lower  $\xi/E$ , meaning that the stack-up voltage  $\xi$  should be kept to minimum, as would be expected intuitively.

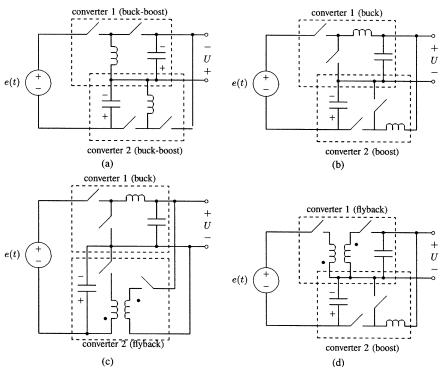

Fig. 3. (a) and (b) Examples of simple input-rectifierless ac/dc converters. A flyback converter needed in (c) and (d) in lieu of buck-boost converter to reverse voltage polarity.

# III. CIRCUIT IMPLEMENTATION OF SIMPLE AC/DC **CONVERTERS**

The implementation of an ac/dc converter based on the foregoing configuration can be proceeded by inserting appropriate dc/dc converters to the model. Fig. 3(a) shows a nonisolated ac/dc converter which is constructed with the buck-boost converter serving as both converters 1 and 2, and Fig. 3(b) shows another nonisolated ac/dc converter which is constructed with a buck converter and a boost converter serving as converters 1 and 2, respectively. Note that in Fig. 3(c) and (d), the flyback converter achieves polarity reversal, and does not provide isolation for the entire ac/dc converter unless the other dc/dc converter is also isolated.

# IV. EXTENSION OF BASIC TOPOLOGIES

The same idea can be implemented with higher-order dc/dc converters. For example, the Cuk converter has two possible dc outlets which can be used as input to converter 2, as described in Section II. Likewise, the zeta and SEPIC converters can serve the purpose. Fig. 4 shows the conceptual arrangement.

Suppose converter 1 (labeled as DC/DC-1 in Fig. 4) has an extra output voltage U' which can be used to feed converter 2 (labeled as DC/DC-2). Let  $k_{11}$ ,  $k_{12}$  and  $k_2$  be the voltage ratios defined as

$$k_{11} = \frac{U}{e(t) + \xi}$$

$$k_{12} = \frac{U'}{e(t) + \xi}$$

(16)

$$k_{12} = \frac{U'}{e(t) + \xi} \tag{17}$$

$$k_2 = \frac{\xi}{U'}. (18)$$

Fig. 4. Implementation of input-rectifierless ac/dc converter using higher-order dc/dc converters (DC/DC-1 can be Ćuk, SEPIC or zeta converter).

The constraints imposed on the voltage ratios can be derived in a similar manner as in Section II. First of all,  $\xi$  must be larger than E, i.e.,

$$k_2 > \frac{E}{U'}. (19)$$

Moreover,  $k_{11}$  and  $k_{12}$  are not independent. For the Ćuk converter, for example, we have  $1 + k_{11} = k_{12}$ , which means

$$U' = U + e(t) + \xi$$

with  $Cuk$  as converter 1. (20)

Obviously, we have U' > U, since e(t) > -E for all time. Thus, (19) becomes

$$k_2 > \frac{E}{U}$$

with  $\acute{C}uk$  as converter 1. (21)

So, if E > U, converter 2 should be a step-up converter; otherwise it can be either a step-up or step-down converter. As for converter 1, we observe that

$$\frac{U}{\xi + E} < k_{11} < \frac{U}{\xi - E}.$$

(22)

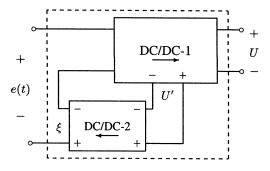

Fig. 5. Outline of two possible control approaches.

Thus, if  $U/(\xi+E)>1$ , converter 1 must be a step-up converter; if  $U/(\xi-E)<1$ , converter 1 must be a step-down converter; and if  $U/(\xi+E)<1$  and  $U/(\xi-E)>1$ , then converter 1 must be able to do both step-down and step-up at different time in a line cycle. If the Ćuk converter is used, the duty cycle can be controlled to satisfy these conditions.

## V. CONTROL APPROACH

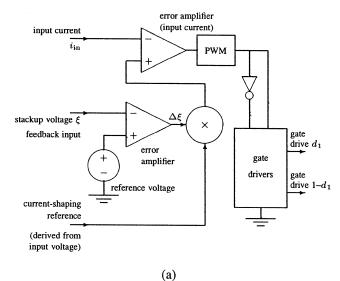

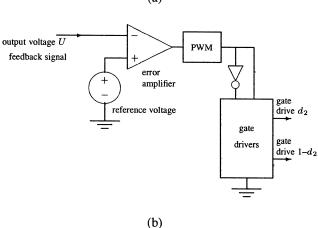

Suppose it is required that the input current be shaped to achieve unity power factor, in addition to a well regulated output voltage [6]–[8]. We may summarize the control requirements as follows.

- To produce a tightly regulated dc output voltage.

- To shape the input current to give unity power factor.

- To crudely control the level of the dc stack-up voltage.

It can be shown theoretically that two separate control parameters are needed to achieve the above requirements [9], [10]. In our circuit, the allowable control parameters are the duty cycles of the two converters. Thus, in general, two control loops should

Fig. 6. Experimental converter circuit based on that of Fig. 3(d).

be designed, one for regulating the output voltage and the other for shaping the input current. Furthermore, since the converters are bi-directional, feedback can be assigned arbitrarily to the converters. Two cases are therefore possible:

- i) Converter 1 shapes the input current while converter 2 regulates the output voltage, as shown in Fig. 5(a).

- ii) Converter 1 regulates the output voltage while converter 2 shapes the input current, as shown in Fig. 5(b).

It is worth noting that the input current waveform can be arbitrarily programmed by implementing suitable control of one of the converters. In the usual application of power factor correction, the converter responsible for shaping the input current can provide crude regulation for the stack-up voltage. This practical case will be illustrated in the experimental prototype to be discussed in Section VI.

## VI. EXPERIMENTAL VERIFICATION

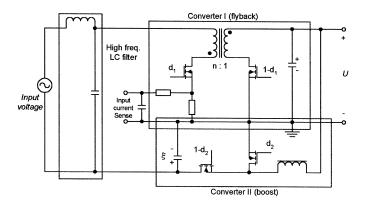

In this section, we report experimental results of a selected ac/dc converter that has been constructed using the afore-described synthesis process. The types of dc/dc converters used are same as the ones shown in Fig. 3(d), i.e.,

Convertor 1 : flyback convertor (turn ratio n:1);

Convertor 2: boost covertor.

Referring to Table III, this particular choice of converter type is suitable for the cases where E>U and  $\xi$  being any value. Moreover, efficiency consideration would suggest a low value for  $\xi$ .

The control consists of two separate feedback loops, as discussed in Section V. In particular, we employ the configuration shown in Fig. 5(a), i.e., an input current shaper applied to the flyback converter and an output regulator applied to the boost converter. The input current shaper also regulates the stack-up voltage  $\xi$ . Figs. 6 and 7 show the experimental converter and the schematic control circuit.

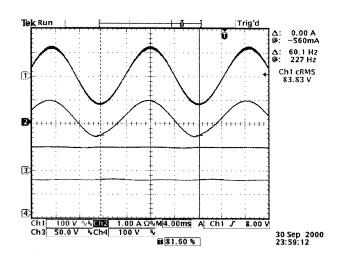

We first report the test results for a 50 Hz line input, which are summarized in Table I for two different choices of  $\xi$ . The waveforms of the input voltage, input current, output voltage and stack-up voltage are shown in Fig. 8. It may be of interest to examine the conversion ratios of the individual converters for different input voltage levels, in order to verify the analytical equations developed in Section II-B. Let  $d_1$  and  $d_2$  be the duty cycle of converter 1 and converter 2, respectively. Then,

Fig. 7. Control circuit for (a) regulating  $\xi$  (crudely) and shaping input current and (b) regulating U (tightly).

TABLE I

EXPERIMENTAL MEASUREMENTS FOR AN INPUT-RECTIFIERLESS AC/DC

CONVERTER USING A FLYBACKCONVERTER AND A BOOST CONVERTER

| Parameters                   | Test 1         | Test 2           |  |

|------------------------------|----------------|------------------|--|

| Input voltage $E$            | 121 V (peak)   | 121 V (peak)     |  |

| Input current $\hat{i}_{in}$ | 0.735 A (peak) | 0.637 A (peak)   |  |

| Output voltage $U$           | 48 V           | 48 V             |  |

| Output current               | 0.7 A          | 0.5 A            |  |

| Flyback turn-ratio           | 1:1            | 3:1              |  |

| Stack-up voltage $\xi$       | 140.83 V       | 199.41 V         |  |

| Power input $P_{\rm in}$     | 44.5 W         | 38.5 W           |  |

| Power output $P_o$           | 33.6 W         | 24 W             |  |

| Efficiency                   | 75.9 %         | 62.3 %           |  |

|                              |                | (consistent with |  |

|                              |                | higher ξ)        |  |

$k_1$  and  $k_2$ , as defined previously, are  $k_1=d_1/n(1-d_1)$  and  $k_2=1/(1-d_2)$ , respectively, where n is the flyback transformer turn ratio. Table II shows the values of duty cycles and

Fig. 8. Waveforms of input voltage, input current, output voltage and stack-up voltage for the rectifierless ac/dc converter operating at 50 Hz line frequency. (a) Test 1 conditions: stack-up voltage = 140 V; and (b) Test 2 condition: stack-up voltage = 204 V. Trace 1: input voltage (100 V/div), Trace 2: input current (1 A/div), Trace 3: output voltage (50 V/div), Trace 4: stack-up voltage  $\xi$  (100 V/div). Note that the apparent dc offset of the input current does not actually exist and can be eliminated by "de-gaussing" the current probe.

(b)

TABLE II

MEASURED DUTY CYCLES AND VOLTAGE RATIOS FOR DIFFERENT INPUT

VOLTAGE LEVELS FOR AN INPUT-RECTIFIERLESS AC/DC CONVERTER USING A

FLYBACK CONVERTER AND A BOOST CONVERTER

|                   | input = -98V |        | input = 0V |        | input = +86V |        |

|-------------------|--------------|--------|------------|--------|--------------|--------|

|                   | Test 1       | Test 2 | Test 1     | Test 2 | Test 1       | Test 2 |

| $\overline{U}$    | 48 V         | 48 V   | 48 V       | 48 V   | 48 V         | 48 V   |

| ξ                 | 142 V        | 204 V  | 140 V      | 202 V  | 139 V        | 198 V  |

| $d_1$             | 0.515        | 0.575  | 0.263      | 0.424  | 0.190        | 0.349  |

| $d_2$             | 0.657        | 0.757  | 0.657      | 0.757  | 0.653        | 0.757  |

| $k_1$             | 1.062        | 0.451  | 0.345      | 0.245  | 0.235        | 0.179  |

| $k_2$             | 2.915        | 4.115  | 2.915      | 4.115  | 2.881        | 4.115  |

| $\frac{k_1k_2}{}$ | 3.096        | 1.856  | 1.04       | 1.008  | 0.677        | 0.737  |

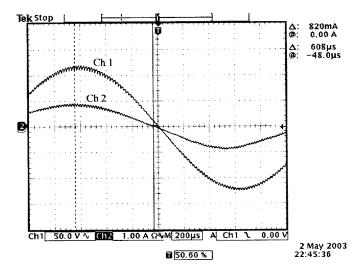

Fig. 9. Waveforms of input voltage and input current at 400 Hz line frequency showing total elimination of zero-crossing distortion, with input voltage = 85 V (rms), stack-up voltage = 147 V, input power = 46.5 W, efficiency = 72.71%. Trace 1: input voltage (50 V/div), Trace 2: input current (1 A/div).

TABLE III CHOICE OF CONVERTERS

| Condition               | Converter 1  | Converter 2  |  |

|-------------------------|--------------|--------------|--|

| E > U                   | _            | step-up      |  |

| E < U                   |              | step-up/down |  |

| $U > \xi + E$           | step-up      | _            |  |

| $U < \xi - E$           | step-down    | -            |  |

| $\xi - E < U < \xi + E$ | step-up/down |              |  |

voltage ratios for a few input voltage levels. Note that at the zero crossing of the input voltage, i.e., e(t)=0, the product of the two conversion ratios is equal to one, as predicted in Section II-B. Also, we observe that the efficiency of the converter drops significantly when the stack-up voltage is large, consistent with our earlier analysis of the power circulation problem.

Finally, to show that the proposed circuit indeed solves the problem of zero-crossing distortion for high line frequencies as reported in Sun [1], we raise the line frequency to 400 Hz and examine the input current waveform. As shown in Fig. 9, the input current is entirely free from zero-crossing distortion.

### VII. CONCLUSION

Most conventional ac/dc converters contain an input rectifier which provides a rectified full-wave input voltage for subsequent processing by one or more converters depending upon the functional requirements [11], [12].

In this paper, we show that dc/dc converters can be used to construct ac/dc converters without the need for input rectifiers. The main purpose of this paper is to point out the basic construction procedure and topological possibilities of creating ac/dc converters out of simple dc/dc converters. In particular, it has been shown that

- two dc/dc converters are sufficient;

- the two dc/dc converters should permit bi-directional power flow;

- the two dc/dc converters should be separately controlled to achieve output regulation and input current shaping;

- some power is being circulated between the two converters.

Furthermore, some design constraints have been discussed, emanating from the limitation of the conversion ratios that can be achieved by particular types of converters. The idea has been experimentally tested with a prototype circuit.

While the present work focuses on the basic synthesis problem, the efficiency issue may be a practical concern. Essentially, since circulating power always exists, loss becomes inevitable and can be quite large if the stack-up dc voltage is not properly controlled. Note that the loss is proprotional to the ratio of the stack-up voltage to the peak input voltage. Thus, as a simple rule, the stack-up voltage should be just above the peak input voltage in order to maintain proper operation.

Finally, as a remark of potential applications, ac/dc converters without input rectifiers are devoid of phase-lead effect and hence can eliminate zero-crossing distortions in power-factor-correction applications. Also, the problem of zero-crossing distortions is particularly serious when the mains frequency is high, as in the case of aircraft power systems. Thus, ac/dc converters without input rectifiers can be used to construct power-factor-correction power supplies for airborne applications. Details of an airborne application will be reported in a future paper.

#### REFERENCES

- J. Sun, "Demystifying zero-crossing distortion in single-phase PFC converters," in *Proc. IEEE Power Electron. Spec. Conf.*, 2001, pp. 1109–1114.

- [2] I. Kim and B. K. Bose, "A new ZCS turn-on and ZVS turn-off unity power factor PWM rectifier with reduced conduction loss and no auxiliary switches," in *Proc. IEEE Power Electron. Spec. Conf.*, 1998, pp. 1344–1350.

- [3] E. Rodriguez, O. Garcia, J. A. Cobos, J. Arau, and J. Uceda, "A single-stage rectifier with PFC and fast regulation of the output voltage," in *IEEE Power Electron. Spec. Conf. Rec.*, 1998, pp. 1642–1648.

- [4] A. Sulistyono and P. N. Enjeti, "A series resonant ac-to-dc rectifier with high-frequency isolation," in *Proc. IEEE Appl. Power Electron. Conf.* Exp., 1994, pp. 379–402.

- [5] A. Ikriannikov and S. Ćuk, "Direct ac/dc conversion without input rectification," in *Proc. IEEE Power Electron. Spec. Conf.*, 1999, pp. 181–186.

- [6] C. Zhou and M. Jovanović, "Design trade-offs in continuous current-mode controlled boost power-factor correction circuits," in *Proc. High Freq. Power Conv. Conf.*, 1992, pp. 209–220.

- [7] R. Redl, "Power-factor correction in single-phase switching-mode power supplies," *Int. J. Electron.*, vol. 77, no. 5, pp. 555–582, 1994.

- [8] C. Andrieu, J. P. Ferrieux, and M. Rocher, "The ac/dc stage: A survey of structures and chopper control modes for power factor correction," *EPE J.*, vol. 5, no. 3/4, pp. 17–22, 1996.

- [9] C. K. Tse and M. H. L. Chow, "Theoretical study of switching converters with power factor correction and output regulation," *IEEE Trans. Circuits Syst. I*, vol. 47, pp. 1047–55, July 2000.

- [10] C. K. Tse, "Circuit theory of power factor correction in switching converters," *Int. J. Circuit Theory Appl.*, vol. 31, no. 2, pp. 157–198, 2003.

- [11] R. Erickson, M. Madigan, and S. Singer, "Design of simple high power factor rectifier based on the flyback converter," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 1990.

- [12] L. Dixon, "High power factor preregulator for offline power supply," in *Unitrode Switching Regulated Power Supply Design Seminar Manual*. New York: Unitrode, 1990, pp. 12.1–12.

C. P. Liu (M'99) was born in Hong Kong in 1970. He received the B.S. degree in electrical and electronic engineering from the University of Hong Kong, in 1993

From 1993 to 1999, he held several industrial positions in switching power supply design. Since 1999, he has been with the Power Electronics Laboratory, University of Hong Kong, where he is a Principal Engineer. His research interest includes switching converter topologies, synchronous rectifiers, soft switching, and EMI modeling.

tors.

N. K. Poon (M'95) received the B.Eng. degree (with honors) in electronic engineering from the City University of Hong Kong, in 1995, and the Ph.D. degree from Hong Kong Polytechnic University, in 2003.

After graduation, he worked with Artesyn Technologies (Asia Pacific) Limited for three and a half years before joining the Power Electronics Laboratory, University of Hong Kong. His current interest includes soft switching techniques, EMI modeling, PFC topologies, synchronous rectification, converter modeling, PWM inverters, and fast transient regula-

**Chi K. Tse** (M'90–SM'97) received the B.Eng. degree (with first class honors) in electrical engineering and the Ph.D. degree from the University of Melbourne, Australia, in 1987 and 1991, respectively.

He is a Professor with Hong Kong Polytechnic University, and his research interests include chaotic dynamics and power electronics. He is the author of *Linear Circuit Analysis* (London, U.K.: Addison-Wesley 1998) and *Complex Behavior of Switching Power Converters* (Boca Raton, FL: CRC

Press, 2003), co-author of *Chaos-Based Digital Communication Systems* (Heidelberg, Germany: Springer-Verlag, 2003) and co-holder of a U.S. patent. Since 2002, he has been an Advisory Professor with the Southwest China Normal University, Chongqing, China.

Dr. Tse received the L.R. East Prize from the Institution of Engineers, Australia, in 1987, the IEEE Transactions on Power Electronics Prize Paper Award, in 2001, the President's Award for Achievement in Research, and the Faculty's Best Researcher Award. He was an Associate Editor for the IEEE Transactions on Circuits and Systems Part I—Fundamental Theory and Applications, from 1999 to 2001, and, since 1999, has been an Associate Editor for the IEEE Transactions on Power Electronics.

**Bryan M. H. Pong** (M'84–SM'96) was born in Hong Kong. He received the B.Sc. degree in electronic and electrical engineering from the University of Birmingham, U.K., in 1983 and the Ph.D. degree in power electronics from Cambridge University, U.K., in 1987.

After graduation, he became a Senior Design Engineer and then a Chief Design Engineer at National Semiconductor Hong Kong, where he was involved in electronic product design. Afterwards he joined ASTEC International, Hong Kong, first as a Principal

Engineer and then a Division Engineering Manager. He is now an Associate Professor with the University of Hong Kong, where he is in charge of the Power Electronics Laboratory and leads a team to carry out research in switching power supplies. His research interests include synchronous rectification, EMI issues, power factor correction, magnetic component design and soft switching. He co-holds a number of U.S. patents.

Y. M. Lai (M'92) received the B.Eng. (with honors) degree in electrical engineering from the University of Western Australia, Perth, Australia, in 1983, the M.Eng.Sc. degree in electrical engineering from University of Sydney, Sydney, Australia, in 1986, and the Ph.D. degree from Brunel University, U.K., in 1997.

He is an Assistant Professor with Hong Kong Polytechnic University, Hong Kong, and his research interests include computer-aided design of power electronics and nonlinear dynamics. Prior to joining the University, he held technical positions with National

Semiconductor, Derek Philips Associates, and Siliconix Hong Kong Limited.