## Self-organized Ge nanocrystals embedded in HfAlO fabricated by pulsed-laser deposition and application to floating gate memory

W. L. Liu

Department of Applied Physics, The Hong Kong Polytechnic University, Hong Kong, China and The Research Center of Semiconductor Functional Film Engineering Technology, State Key Laboratory of Functional Materials for Informatics, Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, 865 Changning Road, Shanghai, 200050, China

P. F. Lee, J. Y. Dai, <sup>a)</sup> J. Wang, H. L. W. Chan, and C. L. Choy *Department of Applied Physics, The Hong Kong Polytechnic University, Hong Kong, China*

## Z. T. Song and S. L. Feng

The Research Center of Semiconductor Functional Film Engineering Technology, State Key Laboratory of Functional Materials for Informatics, Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, 865 Changning Road, Shanghai, 200050, China

(Received 27 July 2004; accepted 5 November 2004; published online 28 December 2004)

A trilayer metal-oxide-semiconductor structure containing a HfAlO tunnel layer, isolated Ge nanocrystals, and a HfAlO control layer, was obtained using pulsed-laser deposition (PLD). Self-organized Ge nanocrystals were formed by PLD at 600 °C, suggesting a useful low-temperature process for fabricating Ge nanocrystals embedded in dielectric materials. The self-organized Ge nanocrystals so formed were uniform in size and distribution with a density approaching 10<sup>12</sup> cm<sup>-2</sup>. The effects of deposition temperature and growth rate in forming Ge nanocrystals were investigated and it was revealed that a relatively low temperature and growth rate are favorable for the formation of Ge nanocrystals. The memory effect of the Ge nanocrystals with storage charge density of up to 10<sup>12</sup> cm<sup>-2</sup> has been demonstrated by the presence of hysteresis in the capacitance-voltage curves. © 2005 American Institute of Physics. [DOI: 10.1063/1.1846154]

The nanocrystal floating gate embedded in dielectrics has attracted a great deal of attention recently because it can potentially be applied in nonvolatile, high-speed, highdensity, and low-power consuming memory. 1-15 Compared to conventional floating gate memories such as flash, a device composed of nanocrystals isolated by dielectrics benefits from a relatively low operating voltage, high endurance, fast write-erase speeds, and better immunity to soft errors. For the first nano-floating-gate memory, the materials of nanocrystals and dielectrics were Si and SiO<sub>2</sub>, respectively. In recent years, several new memory nodes such as Ge, SiGe, Au, TiN, and Ag have been investigated, and some of them were incorporated with high-k dielectrics. <sup>3–14</sup> The Ge nanocrystal is considered to be an ideal memory node due to its relatively small band gap compared to Si and compatibility with current complementary metal-oxide-semiconductor (CMOS) technology. However, it is still difficult to fabricate uniform and self-organized Ge nanocrystals. Most of the methods, including the thermal annealing of Ge and dielectric mixture layer, <sup>13–15</sup> Ge ion implantation, <sup>5</sup> and the oxidation of SiGe, <sup>6,7</sup> require annealing at high temperatures. Baron et al. 16 has fabricated Ge nanodots on the SiO<sub>2</sub> matrix by low-pressure chemical vapor deposition. However, silicon nuclei are needed in this method. Pulsed-laser deposition (PLD) is a good method for growing high-quality structures at low temperatures. Hassan et al. 17 employed it to fabricate Ge nanocrystals embedded in an AlN matrix for optical application. In this Letter, we report on the formation of selforganized Ge nanocrystals at relatively low substrate temperatures using PLD, and the memory effect of the metal-

oxide-semiconductor (MOS) structure composed of Pt electrode, a HfAlO control gate, Ge nanocrystals, and a HfAlO tunnel layer on Si substrate. The motivation for integrating the Ge nanocrystals with HfAlO is its potential for implementation in the new generation CMOS technology. In fact, recent studies have shown that high-*k* dielectrics, instead of SiO<sub>2</sub>, for the tunnel layer in nanocrystal floating gate memory can also improve the tradeoff between the data retention and program efficiency due to the unique band asymmetry of high-*k* dielectrics in the programming and retention modes. In addition, our earlier works have shown that HfAlO is a promising high-*k* material because of its thermal stability. Is

A pulsed excimer laser with multiple targets was used to deposit HfAlO films and Ge nanocrystals, where the atomic ratio of HfO<sub>2</sub> to Al<sub>2</sub>O<sub>3</sub> in the composite target was 1:2. The laser fluence and frequency used were 5 J/cm<sup>2</sup> and 2 Hz, respectively. A 7-nm-thick tunnel HfAlO layer was first grown on a P-type (100) Si substrate at 550 °C. Subsequently, the Ge nanocrystals were deposited on the surface of the HfAlO at 600 °C. Different deposition time and substrate temperatures were implemented in order to study their effects on the formation of Ge nanocrystals. The memory structure used in this study is a MOS capacitor with a dielectric stack made up of Ge nanocrystals sandwiched between the tunnel and control HfAlO layers. The control HfAlO layer, with a thickness of 10 nm, was deposited at 550 °C. The samples were finally annealed at 800 °C for 30 min in N<sub>2</sub> ambient, and Pt dot electrodes with a diameter of 0.2 mm were subsequently deposited by PLD.

Ge nanocrystals were characterized by atomic force microscopy (AFM) and scanning electron microscopy (SEM) before the deposition of the control layer. Trilayer structures

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed; electronic mail: apdaijy@inet.polyu.edu.hk

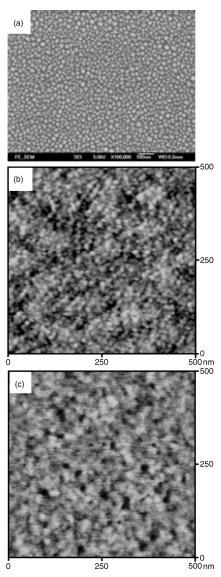

FIG. 1. SEM picture of high-density self-organized Ge nanocrystals deposited on (a) HfAlO matrix by PLD for 1 min at 600 °C, and AFM images of Ge nanocrystals on HfAlO matrix by PLD for 30 s at (b) 600 °C and (c) 700 °C.

were investigated by high-resolution transmission electron microscopy (TEM). The memory effect in Ge nanocrystal-embedded capacitors fabricated by PLD was characterized by measurements of capacitance voltage (C-V) and current voltage (I-V).

Figure 1(a) shows a typical SEM image of Ge nanocrystals grown at 600 °C. It can be seen that Ge nanocrystals are well self-organized and distribute uniformly. The density and mean size of the dots are about  $8 \times 10^{11}$  cm<sup>-2</sup> and 25 nm, respectively. The island structure of the Ge suggests that the growth is based on the Volmer-Webber mode, where Ge atoms can easily combine with each other but not with HfAlO on Si in our experimental conditions. The most remarkable difference between PLD and other vapor deposition methods is the high energy of the plasma generated by the laser ablation of the desired target material. Therefore, during PLD the Ge plasma has a relatively high forward velocity, which leads to the relatively uniform distribution of Ge nanocrystals. According to the observation by cross-sectional TEM (not shown here), the height of these nanocrystals is about 25 nm, resulting in an increased surface roughness on the top dielectric that hinders the application of nanocrystal floating

FIG. 2. High-resolution TEM images of samples composed of HfAlO control gate, Ge nanocrystals, and HfAlO tunnel layer on Si substrate: (a) asgrown and (b) annealed at  $800\,^{\circ}$ C.

gate memory. Therefore, the deposition time of Ge has been reduced accordingly in the following experiments.

The substrate temperature was found to be an important parameter for the growth of Ge nanocrystals. Figures 1(b) and 1(c) show AFM images of the Ge nanocrystals grown at the temperatures of 600 and 700 °C, respectively. From Fig. 1(b), it can be seen that the Ge nanocrystals are well self-organized and their diameter is about 10 nm. By contrast, the diameter of the Ge nanocrystals deposited at 700 °C, as shown in Fig. 1(c), is larger and their height becomes smaller. This suggests that when the substrate temperature increases, the diffusion coefficient of Ge atoms also increases, and the Ge atoms are relatively easier to combine with the HfAlO atoms. Therefore, the substrate temperature of 600 °C for the growth of Ge nanocrystals has been used to fabricate memory capacitors.

The structure of the memory capacitor was investigated by cross-sectional TEM. Figure 2(a) shows the structure of the as-grown samples containing three obvious layers on silicon substrate, i.e., the HfAlO control layer, the Ge nanocrystals layer, and the HfAlO tunnel layer. The Ge nanocrystals indicated by white circles are uniformly distributed between the HfAlO control layer and the tunnel layer. The thicknesses of the tunnel layer and the control layer are about 7 and 14 nm, respectively. From the high-resolution TEM image, as shown in Fig. 2(a), it can be seen that the HfAlO layers have an amorphous structure and the Ge nanocrystals are single crystalline. The lattice fringes that were observed are identified as {111} planes of Ge. Our experimental results showed that the growth rate can also affect the crystallinity of the Ge nanocrystals. When the growth rate is higher, the

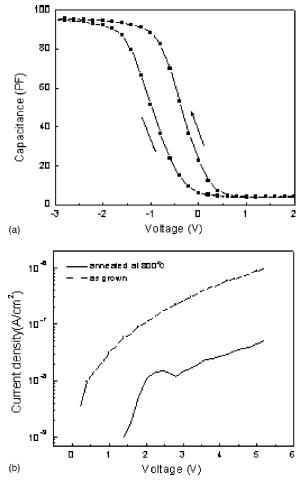

FIG. 3. (a) High-frequency (1-MHz) C-V curves and (b) I-V curves of as-grown and 800  $^{\circ}$ C annealed MOS capacitors.

Ge nanocrystals are amorphous. It can also be seen from Fig. 2(a) that the Ge nanocrystals are spherical in shape and their diameter is about 10 nm, which is consistent with the AFM result shown in Fig. 1(b). The interface between the HfAlO tunnel layer and the silicon substrate is almost free from any interfacial layer. Figure 2(b) is the high-resolution TEM image of the MOS structure annealed at 800 °C. It can be clearly seen that even after annealing at 800 °C, the interface between the HfAlO tunnel layer and the silicon substrate is still sharp and is free from any interfacial layer. It can also be seen that after annealing at 800 °C, the Ge nanocrystals increased in size. Some crystal lattices in the control layer may be due to the diffusion of Ge. It is also worth noting that the existence of Ge and Ge diffusion may decrease the crystallization temperature of HfAlO and lead to localized crystallization. The detailed mechanism should be studied further.

The *C-V* measurement of the as-grown and 800 °C annealed MOS capacitors incorporating the Ge nanocrystals revealed that the as-grown sample exhibits abnormal *C-V* characteristics (not shown) and the sample annealed at 800 °C presents a significant hysteresis, indicating successful charge storage. Figure 3(a) shows the high-frequency (1-MHz) *C-V* curve of the sample annealed at 800 °C. Anti-clockwise hysteresis indicates electron trapping in the capacitor. The effect of the mobile ions on the charge trapping can be ruled out, since no hysteresis was observed in the control sample without Ge nanocrystals under our experimental conditions and no obvious deformation can be observed in the *C-V* curves as shown in Fig. 3(b). The flatband voltage shift is

about 0.6 V. Calculated by the formula in Refs. 1 and 19, the stored charge density is up to  $10^{12}$  cm<sup>-2</sup>.

The different C-V characteristics between the as-grown and the annealed samples can be understood by measuring their leakage currents. Figure 3(b) shows the leakage currents of the two samples with and without annealing. It can be seen that the leakage current of the memory structure annealed at 800 °C is very small and it is much smaller than that of the sample without annealing. The relatively large leakage current of the sample without annealing is due to the presence of a large amount of oxygen vacancies in the asgrown HfAlO films. Annealing at 800 °C in a quartz tube reduced the oxygen vacancies and the leakage current.

In summary, we have fabricated at relatively low temperature by PLD method a memory structure containing a HfAlO control gate, well self-organized Ge nanocrystals, and a HfAlO tunnel layer. The substrate temperature and growth rate were found to be the key factors influencing the size and distribution of the Ge nanocrystals. The obvious memory effect of the trilayer structure was demonstrated by the presence of hysteresis in the C-V curves with a storage charge density of up to  $10^{12}$  cm<sup>-2</sup>.

This work was supported by the Hong Kong Polytechnic University Central Grant (G-YD55), the Chinese Natural Science Foundation (Grant No. 60201004), and the Shanghai Science Committee Foundation (Grants No. 03DE11009 and 04QMX1463).

<sup>1</sup>S. Tiwari, F. Rana, H. Hanafi, A. Hartstein, E. F. Crabbe, and K. Chan, Appl. Phys. Lett. **84**, 1377 (1996).

<sup>2</sup>X. Tang, X. Baie, J. P. Colinge, A. Crahay, B. Katschmarsyj, V. Scheuren, D. Spote, N. Reckinger, F. Van de Wiele, and V. Bayot, Solid-State Electron. **44**, 2259 (2000).

<sup>3</sup>R. Gupta, W. J. Yoo, Y. Wang, Z. Tan, G. Samudra, S. Lee, D. S. H. Chan, K. P. Loh, L. K. Bera, N. Balasubramanian, and D. L. Kwang, Appl. Phys. Lett. **84**, 4331 (2004).

<sup>4</sup>M. Kanoun, A. Souifi, T. Baron, and F. Mazen, Appl. Phys. Lett. **84**, 5079 (2004).

<sup>5</sup>H. I. Hanafi, S. Tiwari, and I. Khan, IEEE Trans. Electron Devices **43**, 9 (1996).

<sup>6</sup>T. Sass, V. Zela, A. Gustafsson, I. Pietzonka, and W. Seifert, Appl. Phys. Lett. **81**, 3455 (2002).

<sup>7</sup>Y. C. King, T. J. King, and C. Hu, IEEE Trans. Electron Devices **48**, 696

<sup>8</sup>D. W. Kim, T. Kim, and S. K. Banerjee, IEEE Trans. Electron Devices **50**, 1823 (2003).

<sup>9</sup>J. J. Lee, X. Wang, W. Bai, N. Lu, and D. L. Kwong, IEEE Trans. Electron Devices **50**, 2067 (2003).

<sup>10</sup>S. Paul, C. Pearson, A. Molloy, M. A. Cousins, M. Green, S. Kolliopoulou, P. Dimitrakis, P. Normand, D. Tsoukalas, and M. C. Petty, Nano Lett. 3, 533 (2003).

<sup>11</sup>Q. Wan, Z. T. Song, W. L. Liu, C. L. Lin, and T. H. Wang, Appl. Surf. Sci. 230, L8 (2004).

<sup>12</sup>T. Usuki, T. Futatsugi, and N. Yokoyama, Microelectron. Eng. **47**, 281

<sup>13</sup>Q. Wan, C. L. Lin, W. L. Liu, and T. H. Wang, Appl. Phys. Lett. **82**, 4708 (2003).

<sup>14</sup>Q. Wan, N. L. Zhang, W. L. Liu, C. L. Lin, and T. H. Wang, Appl. Phys. Lett. 83, 138 (2003).

<sup>15</sup>Y. Q. Wang, J. H. Chen, W. J. Yoo, Y. C. Yeo, S. J. Kim, R. Gupta, Z. Y. L. Tan, D. L. Kwong, A. Y. Du, and N. Balasubramanian, Appl. Phys. Lett. 84, 5407 (2004).

<sup>16</sup>T. Baron, B. Pelissier, L. Perniola, F. Mazen, J. M. Hartmann, and G. Rolland, Appl. Phys. Lett. 83, 1444 (2003).

<sup>17</sup>K. M. Hassan, A. K. Sharma, J. Narayan, J. F. Muth, C. W. Teng, and R. M. Kolbas, Appl. Phys. Lett. **75**, 1222 (1999).

<sup>18</sup>P. F. Lee, J. Y. Dai, K. H. Wong, H. L. W. Chan, and C. L. Choy, J. Appl. Phys. **93**, 3665 (2003).

<sup>19</sup>J. K. Kim, H. J. Cheong, Y. Kim, J.-Y. Yi, H. J. Bark, S. H. Bang, and J. H. Cho, Appl. Phys. Lett. **82**, 2527 (2003).

Applied Physics Letters is copyrighted by the American Institute of Physics (AIP). Redistribution of journal material is subject to the AIP online journal license and/or AIP copyright. For more information, see http://ojps.aip.org/aplo/aplcr.jsp