## Defect states and charge trapping characteristics of HfO<sub>2</sub> films for high performance nonvolatile memory applications

Cite as: Appl. Phys. Lett. **105**, 172902 (2014); https://doi.org/10.1063/1.4900745 Submitted: 04 April 2014 . Accepted: 16 October 2014 . Published Online: 29 October 2014

Y. Zhang, Y. Y. Shao, X. B. Lu, M. Zeng, Z. Zhang, X. S. Gao, X. J. Zhang, J.-M. Liu, and J. Y. Dai

## ARTICLES YOU MAY BE INTERESTED IN

Charge trapping properties of the  ${\rm HfO_2}$  layer with various thicknesses for charge trap flash memory applications

Applied Physics Letters 96, 093506 (2010); https://doi.org/10.1063/1.3337103

Ferroelectricity in hafnium oxide thin films

Applied Physics Letters 99, 102903 (2011); https://doi.org/10.1063/1.3634052

Defect energy levels in HfO<sub>2</sub> high-dielectric-constant gate oxide

Applied Physics Letters 87, 183505 (2005); https://doi.org/10.1063/1.2119425

## Defect states and charge trapping characteristics of HfO<sub>2</sub> films for high performance nonvolatile memory applications

Y. Zhang, <sup>1</sup> Y. Y. Shao, <sup>1</sup> X. B. Lu, <sup>1,a)</sup> M. Zeng, <sup>1</sup> Z. Zhang, <sup>1</sup> X. S. Gao, <sup>1</sup> X. J. Zhang, <sup>2</sup> J.-M. Liu, <sup>2,b)</sup> and J. Y. Dai<sup>3</sup>

<sup>1</sup>Institute for Advanced Materials and Laboratory of Quantum Engineering and Quantum Materials, South China Normal University, Guangzhou 510006, China

<sup>2</sup>Laboratory of Solid State Microstructures and Innovation Center for Advanced Microstructure, Nanjing University, Nanjing 210093, China

(Received 4 April 2014; accepted 16 October 2014; published online 29 October 2014)

In this work, we present significant charge trapping memory effects of the metal-hafnium oxide-SiO<sub>2</sub>-Si (MHOS) structure. The devices based on 800 °C annealed HfO<sub>2</sub> film exhibit a large memory window of  $\sim$ 5.1 V under  $\pm$ 10 V sweeping voltages and excellent charge retention properties with only small charge loss of  $\sim$ 2.6% after more than 10<sup>4</sup> s retention. The outstanding memory characteristics are attributed to the high density of deep defect states in HfO<sub>2</sub> films. We investigated the defect states in the HfO<sub>2</sub> films by photoluminescence and photoluminescence excitation measurements and found that the defect states distributed in deep energy levels ranging from 1.1 eV to 2.9 eV below the conduction band. Our work provides further insights for the charge trapping mechanisms of the HfO<sub>2</sub> based MHOS devices. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4900745]

Recently, charge trapping flash (CTF) type memory using a dielectric layer as the charge storage medium has received great attentions as a promising memory technology to replace the traditional floating-gate memories. 1-6 In comparison with the conventional poly-silicon floating gate flash memory, they offer the advantages of smaller cell size, lower program/erase (P/E) voltage, and better reliability. 1-6 The well known CTF type memory is the silicon-oxide-nitridesilicon (SONOS) structure based device.<sup>3,4</sup> Although it has been well developed in recent years, it still suffers from the trade-off between programming speed and data retention: ',8 on the one hand, thin tunnel oxide layer can enhance the write/erase speed of the SONOS memory device; on the other hand, thicker tunnel oxide can elongate the retention time. To solve these problems in SONOS type CTF memory, CTF memory devices using high-k materials such as HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, etc., have been developed in recent years. <sup>9-15</sup> These devices can provide large band offset with respect to Si, high trap density, and small equivalent oxide thickness (EOT). Therefore, the CTF memory device with high-k film is expected to offer better device performance as compared to the conventional CTF device with Si<sub>3</sub>N<sub>4</sub> film.

In this paper, we investigate the memory characteristics of high-*k* HfO<sub>2</sub> based CTF memory device of Au/HfO<sub>2</sub>/SiO<sub>2</sub>/Si (MHOS), where the HfO<sub>2</sub> layer works as both charge-trapping oxide and block oxide. Although CTF memory devices without block oxide have been studied by several groups,<sup>7,16</sup> the charge trapping characteristics and mechanisms are still not well understood, and the reported electrical properties remain relatively low. Our present work further clarifies the charge trapping mechanisms of the MHOS memory devices and demonstrates the excellent memory characteristics obtained by a simple fabrication procedure.

P-type Si (100) substrates with  $\rho = 1-10 \Omega$  cm were first cleaned by wet-chemical solution and then dipped in a diluted HF solution (1%) to remove the surface oxide; the wafers were then immediately loaded into a vacuum chamber for deposition. The HfO2 film was deposited by electronbeam evaporation with the substrate temperature of 300 °C. The film thickness was in-situ monitored by a crystal thickness monitor and a typical growth rate was around 0.01 nm/s. After deposition, the HfO2 films were annealed at high temperatures of 800 °C and 875 °C in O2 atmosphere for 5 min by rapid thermal annealing. For measurements of the electrical properties, dot-shaped Au top electrodes with an area of  $\sim 3.14 \times 10^{-4}$  cm<sup>2</sup> were deposited on the surface of the samples using a shadow mask by vacuum evaporation. The electrical properties of the Au-HfO<sub>2</sub>-SiO<sub>2</sub>-Si capacitors were investigated by an Agilent E4980A impedance analyzer and an Agilent B1500A high-precision semiconductor analyzer at room temperature. High-resolution transmission electron microscopy (HRTEM) was used to study the microstructure of the HfO<sub>2</sub> films. The photoluminescence (PL) and photoluminescence excitation (PLE) measurements were carried out to investigate the features of the defect states in the HfO<sub>2</sub> films.

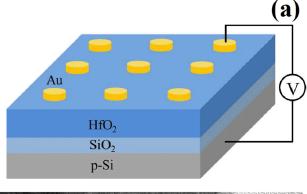

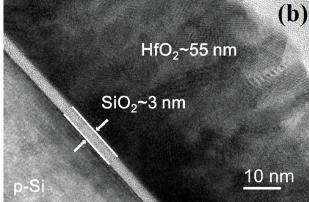

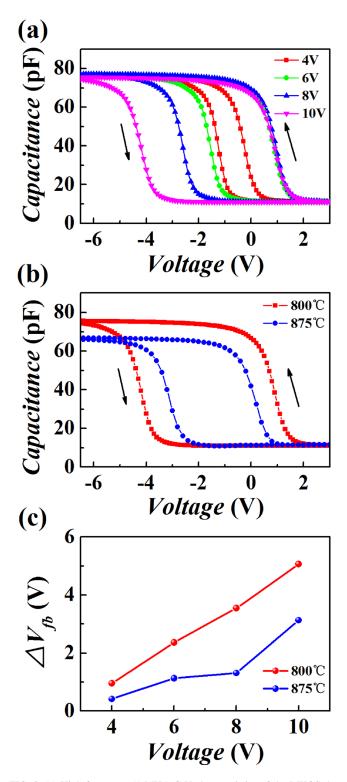

Figure 1(a) schematically represents the MHOS memory device, where the  $HfO_2$  film was fabricated directly on the HF etched silicon substrate under  $\sim 4.0 \times 10^{-4} \, \mathrm{Pa}$  vacuum. The as-deposited  $HfO_2$  film was annealed at high temperature in  $O_2$  ambient by rapid thermal annealing, in order to reduce the leakage current. Figures 1(b) and 1(c) show the cross-sectional TEM images of the  $HfO_2$  films annealed at  $800\,^{\circ}\mathrm{C}$  and  $875\,^{\circ}\mathrm{C}$ , respectively. Both the high-k  $HfO_2$  films show a fully polycrystalline characteristic and a thickness of  $\sim 55\,\mathrm{nm}$ . Between the  $HfO_2$  film and the Si substrate, an amorphous  $SiO_2$  layer is clearly observed. The  $SiO_2$  layer's thickness is  $\sim 3.0\,\mathrm{nm}$  for the sample annealed at  $800\,^{\circ}\mathrm{C}$ , while it is  $\sim 3.9\,\mathrm{nm}$  for the sample annealed at  $875\,^{\circ}\mathrm{C}$ . The interfacial

<sup>&</sup>lt;sup>3</sup>Department of Applied Physics, The Hong Kong Polytechnic University, Hong Kong, China

a)Electronic mail: luxubing@scnu.edu.cn

b)Electronic mail: liujm@nju.edu.cn

FIG. 1. A schematic diagram of the MHOS device structure (a); cross-sectional HRTEM images for  $HfO_2$  films annealed at  $800\,^{\circ}C$  (b) and  $875\,^{\circ}C$  (c).

SiO<sub>2</sub> layer is undesirable for obtaining small EOT when the high-k dielectrics are used as gate dielectric for metal-oxidesilicon field effect transistor<sup>17</sup> or buffer layer for ferroelectric-gate field effect transistor<sup>18</sup> applications. However, this interfacial SiO2 layer during high-k oxide growth or annealing plays a critical role to obtain good electrical properties of the present MHOS devices. The MHOS devices without SiO<sub>2</sub> tunnel oxide layer were also fabricated by using room temperature deposited HfO<sub>2</sub> film without annealing process. Although large memory window was observed, the charge retention time of the MHOS devices was shorter than 10 min (data not shown here). Furthermore, the TEM results also indicate that the SiO<sub>2</sub> tunnel oxide thickness can be controlled by the annealing temperature, which does not require additional processes as used in the previous work. Our present results provide a very simple and low cost method for fabricating the MHOS memory devices.

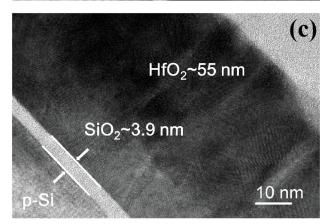

To study the memory properties of the Au/HfO<sub>2</sub>/SiO<sub>2</sub>/Si devices, the high frequency (1 MHz) capacitance-voltage (CV) measurements were carried out at room temperature. Figure 2(a) shows the typical CV characteristics of the MHOS devices with HfO<sub>2</sub> film annealed at 800 °C under different sweeping voltages. The anticlockwise direction of the CV hysteresis during positive-negative-positive voltage

FIG. 2. (a) High frequency (1 MHz) C-V characteristics of the MHOS device with HfO<sub>2</sub> film annealed at  $800\,^{\circ}\text{C}$  under different sweeping voltages; (b) typical C-V characteristics of MHOS devices for HfO<sub>2</sub> annealed at  $800\,^{\circ}\text{C}$  and  $875\,^{\circ}\text{C}$ ; (c) impact of annealing temperature on the memory window width of the MHOS devices under different sweeping voltages.

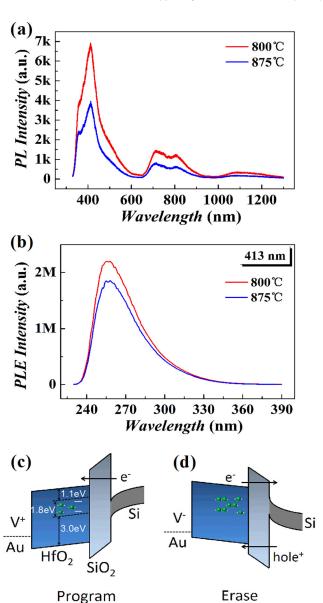

In the tri-layer structure CTF memory devices, the charge trapping mechanisms can be ascribed to the charges trapped in the quantum well, which is formed by the different band offsets of the block oxide, charge trapping oxide, and tunnel oxide. Yet for the present CTF memory devices with a MHOS structure, such a quantum well does not exist as there is no additional block oxide layer and thus cannot be the origin of the significant charge trapping effect. It has been reported that the HfO<sub>2</sub> film naturally has some intrinsic defects such as oxygen vacancies or interstitial oxygen atoms, which induces defect energy levels in the film.<sup>20,21</sup> These defect energy levels are believed to trap charges and to induce the large memory effects. To further investigate the features of the defect states in our electron-beam evaporation deposited HfO2 films, PL and PLE measurements were carried out for the HfO2 films annealed at 800 °C and 875 °C. The HfO<sub>2</sub> films were grown on fused silica substrates and the post deposition annealing processes were performed following the same procedure used in the MHOS structures. As shown in Fig. 3(a), the photoluminescence spectra under 325 nm excitation wavelength exhibit clear PL

FIG. 3. (a) Photoluminescence spectra of  $HfO_2$  films; (b) photoluminescence excitation spectra of the  $HfO_2$  films by monitoring one of the PL peaks at 413 nm (3.0 eV); (c) a schematic diagram of the energy levels of the defect states and the programming process of the MHOS device; (d) a schematic diagram of the erasing process of the MHOS device.

peaks at  $1.4-1.8\,\mathrm{eV}$  and at  $2.1-3.5\,\mathrm{eV}$  for both of the two  $\mathrm{HfO_2}$  films. As the band gap of the  $\mathrm{HfO_2}$  film is around  $5.9\,\mathrm{eV}$ ,  $^{20}$  the PL band at  $1.4-1.8\,\mathrm{eV}$  and at  $2.1-3.5\,\mathrm{eV}$  could not be due to the band-to-band recombination. Instead, it is most probably due to the recombination from defect states to valance band ( $\mathrm{E_V}$ ) or donor defect states to acceptor states, and thus clearly indicated the existence of the high concentration defects in the  $\mathrm{HfO_2}$  films. Furthermore, the sample annealed at  $800\,^{\circ}\mathrm{C}$  has a higher PL intensity than that of the sample annealed at  $875\,^{\circ}\mathrm{C}$ . If we consider that increasing the annealing temperature reduces the oxygen vacancy concentration in the  $\mathrm{HfO_2}$  films, then the PL results also imply that oxygen vacancies or interstitial oxygen atoms should be the dominant source for the defect states.

To further characterize the defect levels, the PLE spectra were measured by monitoring the strongest PL peaks at 413 nm (3.0 eV) of the two same  $\text{HfO}_2$  films. With the

change of the excitation energy, the dominant photoluminescence peak appears at around 258 nm (4.8 eV) excitation energy for both of the two samples. Peaks in the PLE spectra also represent absorption lines of the material. Since the band-to-band absorption is not possible (the band gap of  $HfO_2$  is around 5.9 eV<sup>20</sup>), the 4.8 eV peak in the PLE spectra represents the main defect states lying at 4.8 eV above E<sub>V</sub> of the HfO<sub>2</sub> film. According to the theoretical simulations, the defect states mainly occupy the donor levels rather than the acceptor defect states in the HfO<sub>2</sub> film. <sup>20,21,23</sup> Therefore, the strongest PL peaks at 3.0 eV shown in Fig. 3(a) is assigned to the recombination processes from the donor states at 3.0 eV above E<sub>V</sub> to the E<sub>V</sub> of HfO<sub>2</sub> film. The electrons may first be excited to the defect states of 4.8 eV above  $E_{\rm V}$  and then relaxed to the defect states of 3.0 eV above  $E_{\rm V}$ without radiation. Finally, the relaxed electrons were recombined with the holes in the valence band with a luminance. Summarizing the PL and PLE results, we propose that the dominating defects lie at 4.8 eV above the valence band (that is 1.1 eV below the conduction band), and the defect states are relaxed down to the energy levels of 3.0 eV above the valence band (that is 2.9 eV below the conduction band). The energy level positions of the defect states are schematically shown in Fig. 3(c). Our experimental results on the energy levels of defect states in HfO2 are highly consistent with the theoretical calculation results reported by Xiong et al.<sup>20</sup> and Perevalov et al.<sup>21</sup> In addition to the energy positions of the oxygen vacancies, the physical distribution of the oxygen vacancies was also investigated by the so-called constant current stress (CCS) method.<sup>7</sup> The charge trapping center (i.e., oxygen vacancy centre) is estimated to be 30 nm away from the metal/HfO<sub>2</sub> interface within the HfO<sub>2</sub> dielectric. Based on the PL and PLE analysis, the charge trapping and de-trapping processes can be schematically plotted, as shown in Figs. 3(c) and 3(d). Without fabricating quantum well in the MHOS device structures, the programming and erasing processes can be realized through the efficient charge transfers between the defect states and the silicon substrate.

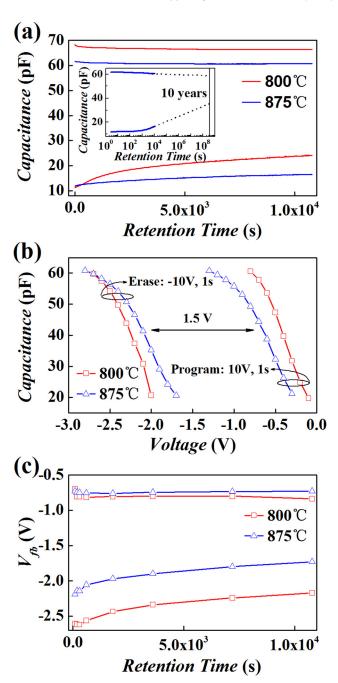

Figure 4(a) shows the charge loss characteristics of the MHOS memory devices. The high and low capacitances are observed at a fixed read voltage of -1 V after a +10 V/1 sprogramming pulse or -10 V/1 s erasing pulse voltage. Excellent charge retention characteristics were observed for both the samples. For example, the high capacitance of 800 °C and 875 °C annealed devices only exhibit ~2.6% and  $\sim 1.5\%$  charge loss after  $10^4$  s of retention. Especially, by extending the retention time to 10 yr by extrapolation, the high and low capacitance of 875 °C annealed sample can still maintain a large difference (as shown in the inset of Fig. 4(a) by using a log-scale of the retention time), indicating a strong charge confinement in the HfO<sub>2</sub> trapping layer. To further investigate the memory retention properties, the flat band voltage (V<sub>fb</sub>) retention characteristics were also investigated. The V<sub>fb</sub> values are extracted from the CV curves measured around flat-band voltage (within this voltage range, there will be no charge trapping and de-trapping process during the CV measurement). Figure 4(b) shows CV characteristics around V<sub>fb</sub> of MHOS devices, indicating clear V<sub>fb</sub> separation after programming and erasing voltage pulses. From the programmed/erased C-V characteristics by pulse

FIG. 4. (a) The long term retention characteristics of the high and low capacitances of the two MHOS devices, the inset shows the 10 yrs' retention extrapolating plot of the 875 °C annealed sample; (b) the C-V curves for  $V_{\rm fb}$  measurement after programming/erasing processes; (c) the long term retention characteristics of  $V_{\rm fb}$  of the two MHOS devices.

voltages,  $V_{fb}$  was measured with a time. Figure 4(c) shows the excellent  $V_{fb}$  retention characteristics for both of the memory devices. Except for the fast decay in the first several minutes, the  $V_{fb}$  values remain very stable even after more than  $10^4$ s retention. It should be mentioned that the sample without any annealing exhibits much worse retention compared to that of the  $800\,^{\circ}\text{C}$  and  $875\,^{\circ}\text{C}$  sample (results not shown), which implies that the  $\text{SiO}_2$  formed during the annealing plays an important role on preventing the charge tunneling back to the Si substrate. The detailed mechanisms will be discussed in the following text.

The excellent charge trapping characteristics of our MHOS devices are believed to originate from the high density

In summary, we have correlatively investigated the charge trapping characteristics and the defect states of the electron-beam-evaporation deposited high-*k* HfO<sub>2</sub> films. The MHOS device structure can be easily constructed by annealing the HfO<sub>2</sub> films at high temperature, and the thickness of the SiO<sub>2</sub> tunnel oxide can be controlled by changing the annealing temperature. The significant memory effects demonstrated in the Au-HfO<sub>2</sub>-SiO<sub>2</sub>-Si devices are attributed to the oxygen vacancies induced defect energy levels in the HfO<sub>2</sub> films, as revealed by PL measurements. Moreover, the MHOS devices exhibit excellent long-term retention properties. Our results demonstrated that the HfO<sub>2</sub> based MHOS

memory device is promising for future flash memory applications.

This work was supported by the National Natural Science Foundation of China (Grant Nos. 61271127, 51472093, and 51431006). Thanks are also given to Hong Kong GRF Grant (No. 514512), the Program for International Innovation Cooperation Platform of Guangzhou (No. 2014J4500016), and Program for Changjiang Scholars and Innovative Research Team in University (Grant No. IRT1243).

<sup>1</sup>H. Reisinger, M. Franosch, B. Hasler, and T. Bohm, Symp. VLSI Technol. Dig. Tech. Pap. **1997**, 113.

<sup>2</sup>I. Fujiwara, H. Aozasa, A. Nakamura, Y. Komatsu, and Y. Hayashi, Tech. Dig. -Int. Electron Devices Meet. **1998**, 995.

<sup>3</sup>M. H. White, D. A. Adams, and J. Bu, IEEE Circuits Devices Mag. 16, 22 (2000).

<sup>4</sup>J. K. Bu and M. H. White, Solid State Electron. **45**, 113 (2001).

<sup>5</sup>X. X. Lan, X. Ou, Y. Q. Cao, S. Y. Tang, C. J. Gong, B. Xu, Y. D. Xia, J. Yin, A. D. Li, F. Yan, and Z. G. Liu, J. Appl. Phys. 114, 044104 (2013).

<sup>6</sup>Z. G. Xu, C. X. Zhu, Z. L. Huo, S. J. Zhao, and M. Liu, J. Phys. D: Appl. Phys. **45**, 185103 (2012).

<sup>7</sup>H. W. You and W. J. Cho, Appl. Phys. Lett. **96**, 093506 (2010).

<sup>8</sup>K. Naruke, S. Taguchi, and M. Wada, Tech. Dig. -Int. Electron Devices Meet. 1988, 424.

<sup>9</sup>S. Choi, M. Cho, H. Hwang, and J. W. Kim, J. Appl. Phys. **94**, 5408 (2003).

<sup>10</sup>Y.-N. Tan, W.-K. Chim, B. J. Cho, and W.-K. Choi, IEEE Trans. Electron Devices **51**, 1143 (2004).

<sup>11</sup>J. Liu, Q. Wang, S. B. Long, M. H. Zhang, and M. Liu, Semicond. Sci. Technol. 25, 055013 (2010).

<sup>12</sup>Y. H. Wu, L. L. Chen, Y. S. Lin, M. Y. Li, and H. C. Wu, IEEE Electron Device Lett. **30**, 1290 (2009).

<sup>13</sup>S. Maikap, T. Y. Wang, P. J. Tzeng, H. Y. Lee, C. H. Lin, C. C. Wang, L. S. Lee, J. R. Yang, and M. J. Tsai, Jpn. J. Appl. Phys., Part 1 47, 1818 (2008).

<sup>14</sup>J. X. Chen, J. P. Xu, L. Liu, and P. T. Lai, Appl. Phys. Lett. **103**, 213507 (2013).

<sup>15</sup>Y. H. Peng, F. Liu, X. Y. Liu, G. Du, and J. F. Kang, Jpn. J. Appl. Phys., Part 1 52, 04CD13 (2013).

<sup>16</sup>E. Hourdakis and A. G. Nassiopoulou, Microelectron. Eng. 88, 1573 (2011).

<sup>17</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. 89, 5243 (2001).

<sup>18</sup>X. B. Lu, K. Maruyama, and H. Ishiwara, J. Appl. Phys. **103**, 044105 (2008)

<sup>19</sup>C. H. Lee, K. C. Park, and K. Kim, Appl. Phys. Lett. **87**, 073510 (2005).

<sup>20</sup>K. Xiong, J. Robertson, M. C. Gibson, and S. J. Clark, Appl. Phys. Lett. 87, 183505 (2005).

<sup>21</sup>T. V. Perevalov, V. S. Aliev, V. A. Gritsenko, A. A. Saraev, and V. Kaichev, Microelectron. Eng. 109, 21 (2013).

<sup>22</sup>S. Maikap, H. Y. Lee, T. Y. Wang, P. J. Tzeng, C. C. Wang, L. S. Lee, K. C. Liu, J. R. Yang, and M. J. Tsai, Semicond. Sci. Technol. 22, 884 (2007).

<sup>23</sup> A. S. Foster, F. L. Gejo, A. L. Shluger, and R. M. Nieminen, Phys. Rev. B. 65, 174117 (2002).

<sup>24</sup>W. Chen, W.-J. Liu, M. Zhang, S.-J. Ding, D. W. Zhang, and M.-F. Li, Appl. Phys. Lett. **91**, 022908 (2007).

<sup>25</sup>J. Robertson, J. Vac. Sci. Technol. B. **18**, 1785 (2000).