# Current Equalizing for a Multi-Modular Current Source Converter

Li Jun, Dehong Xu College of Electrical Engineering Zhejiang University Hangzhou, 310027, P.R. China K.W.E. Cheng

Department of Electrical Engineering

The Hong Kong Polytechnic University

Hong Kong SAR

Abstract - Phase-shifted SPWM technique is adopted to control a directly-paralleled multi-modular current source converter for Super-conducting Magnetic Energy Storage System (SMES) to reach high power and low harmonics. The phase-shifting of the carriers results a serious current unbalance between each converter modules when the high power switch devices work on low switch rate. This paper analyses the problems of the classic current balancing methods and introduces the carrier-swapping method into phase-shifted SPWM technique, to eliminate such current unbalance in a multi-modular current source converter without adjusting the amplitude and phase angle of the modulation waveforms of each module respectively. Experimental results are given to prove the effectiveness of current equalization provided by the carrier-swapping method.

## I. INTRODUCTION

SMES is a perfect component for Flexible AC Transmission System (FACTS) because of its high efficiency and fast response [1],[2]. A bi-direction power converter known as Power Condition System (PCS) is needed by SMES as a tie between the super-conductive coil and the utility system. The PCS can be either a current source converter or a voltage source converter connected to a two-quadrant boost chopper. The super-conductive coil is inherently a current source, the current source converter have more advantages to be the PCS for SMES than the voltage source converter [3],[4],[5].

High power converter is needed for a high power SMES. Current source converter can be paralleled directly to reach high power. Proper PWM control strategy should be applied to such multi-modular current source converter to reduce the harmonic while the switch frequency of the high power device is restricted to a low rate. Phased-shifted SPWM control is a good way to reduce the harmonic and attain linearity characteristics for a multi-modular current source converter [5].

Care should be taken to balance the current of each module in the multi-modular converter. When the carrier frequency is lower (as 3 or 6 times of the modulation signal), the average DC current of each module differs significantly because of the phase shifting of the carriers. A current equalizing control loop is applied to each module to control the amplitude and phase angle of the modulation signal for current balancing [5],[6]. Thus, the modulation signals for each paralleled converter differ from each other seriously, harmonics self-

cancellation originally expected can not be reached pronouncedly [7].

To eliminate the DC current un-balance and AC current distortion result from carrier phase shifting without adjusting the amplitude and phase angle of the modulation waves of each module individually, this paper introduces the carrier-swapping method into phase-shifted SPWM technique for a multi-modular current source converter. Experiment results are given to prove the effectiveness of current equalization provided by the carrier-swapping method.

## II. PHASE SHIFTED SPWM CONTROL WITHOUT CARRIER-SWAPPING

#### A. Main Circuit

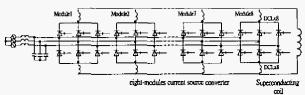

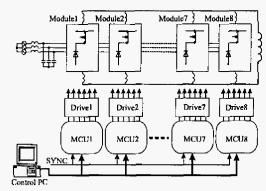

A main circuit of eight-modules current source converter is shown in Fig. 1. Each module is a six-valves current source converter. AC side of each module is connected together directly. DC side of converter module is paralleled through DC inductors.

Figure 1. Main circuit of an eight-modules current source converter for

## B. Phase-shifted SPWM Control

Phase-shifted SPWM control is applied to this multimodular current source converter to reduce harmonics while the switch frequency is low. SPWM control for current source converter need tri-logic signal [8]. The signals are produced as follows:

$$X_{a} = sign \left[ v_{ma} \left( wt \right) - v_{c} \left( w_{s}t + \phi_{s} \right) \right]$$

$$X_{b} = sign \left[ v_{mb} \left( wt \right) - v_{c} \left( w_{s}t + \phi_{s} \right) \right]$$

$$X_{c} = sign \left[ v_{mc} \left( wt \right) - v_{c} \left( w_{s}t + \phi_{s} \right) \right]$$

$$sign \left( x \right) = \begin{bmatrix} 1 & x \ge 0 \\ -1 & x \ge 0 \end{bmatrix}$$

$$Y_{a} = \frac{1}{2} \left( X_{a} - X_{b} \right)$$

$$Y_{b} = \frac{1}{2} \left( X_{b} - X_{c} \right)$$

$$Y_{c} = \frac{1}{2} \left( X_{c} - X_{a} \right)$$

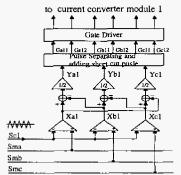

Fig.2 gives the control logic diagram of one converter module. As showing in Fig.2 and Fig.3, the modulation signals of each module are same completely, amplitude of the carrier of each module is equal, the phase angle of the carrier of each module is evenly shifted. In an eight-modules converter, at carrier frequency equal to 3 times of switching frequency, the carrier phase angle difference between adjacent modules is: (360°/3)/8=15°.

Figure 2. Control logic of Phase shifted SPWM

Figure 3. Tri-angle carrier and modulation signal (frequency of carrier is 150Hz)

### C. DC Current Sharing and AC Current Harmonics

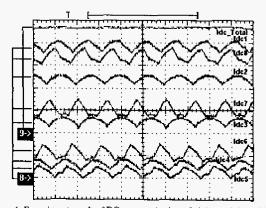

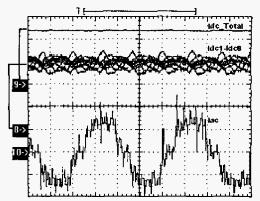

Under such control method, the average DC current of each module is unbalanced badly without current balancing control when the switch frequency is low. An experimental result of DC current sharing of eight modules is given in Fig.4.

Figure 4. Experiment result of DC current sharing of eight modules without current balancing control, M=0.9, α=-90°, frequency of carrier is 150Hz.

Time: 5mS/div, Idc1-Idc8:200mA/div, Idc9:1A/div

Fig.4 shows that this multi-modular converter can not work properly without current balancing control because the current sharing of each module is uneven seriously. Then a

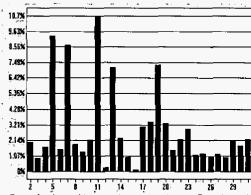

Figure 5(a). Experimental result of DC current of each module, total DC current and AC current with current balance control, Time: 5mS/div, Idc1-Idc8:200mA/div; Idc\_Total, Iac: 2A/div

Figure 5(b). Spectrum of the total AC current with current balance control

current balancing control loop is added in each module, to adjusting the M and  $\alpha$  of the modulation signal of each module to force the DC current to be equalized [4],[5]. Fig.5(a) gives the experimental results of DC current of each modules and the total AC current of eight modules with such control. Fig.5(b) is the harmonics spectrum of AC current. The 5th, 7th, 11th and 13th harmonics are large. Though the control loop can force the current sharing of each module to be balanced, the waveform of the sum of the each module's AC side current is distorted seriously because the modulation signal of each module is different, harmonics then increase.

## III. PHASE SHIFTED SPWM CONTROL WITH CARRIER-SWAPPING

The multi-modular current source converter with carrier phase-shifted SPWM control can obtain a multi-level AC side current waveform with low harmonics based on the prerequisite as following:

- 1) The average DC current of each module should be equal.

- 2) The modulation signal of each module is the same.

- 3) The carrier signal of each module is evenly phase-shifted.

As discussed in the preceding paragraph, if there is no current balancing control, item 2) can be satisfied but item 1)

can not be satisfied; when item 1) is realized with current balancing control mentioned above, item 2) is lost. There is a conflict between item 1) and item 2).

If a current balance control without adjusting M and  $\alpha$  of the modulation signal of each converter module can be found, then the prerequisite item 1) and 2) can be obtained at the same time.

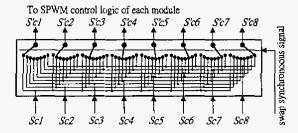

Since the final output of a multi-modular current source converter is the total AC side current and the total DC current, they are the things we real want, we do not care the state of any individual module. At any time, whether the modules 1 to 8 are controlled by carrier signal  $S_{cl}$  to  $S_{c8}$  or controlled by  $S_{c8}$ to  $S_{cI}$  is not the matter, this does not affect the total AC current and the total DC current. If we swap the carrier signal  $S_{cl}$  to  $S_{c\delta}$  between the eight modules at every fixed period  $(T_{swap})$ , this does not affect the total output, but every module has the chance to be controlled by every one of eight carriers lasting  $T_{swap}$  in a period of  $8 \cdot T_{swap}$ . Such carrier swapping method can eliminate the current uneven state in a multimodular converter caused by the carrier phase-shifting. Then current balance control without adjusting M and a of each converter module can be obtained to get the advantage of the harmonic self-cancellation of the phase-shifted SPWM while the switch frequency is low.

## A. Control Logic of Carrier-swapping

Define the swapped carrier as S'ci, then S'ci can be expressed as follow:

$$\begin{split} S'c_i(kT_{swap}) &= Sc_j \\ j &= \begin{cases} \operatorname{mod}(k,n) + i, & \operatorname{mod}(k,n) + i \leq n \\ \operatorname{mod}(k,n) + i - n, & \operatorname{mod}(k,n) + i > n \end{cases} \end{split}$$

n is the number of modules in the multi-modular converter,

$$i=1\sim n$$

$k=0, 1, 2, 3...$

For an eight modules converter, the swap logic can be shown by Fig.6, at every rising edge of the swap synchronous signal, each switch in the Fig.6 is turned to the next position, the moving circle of the switch is:

$$\rightarrow Sc1 \rightarrow Sc2 \rightarrow Sc3 \rightarrow Sc4 \rightarrow Sc5 \rightarrow Sc6 \rightarrow Sc7 \rightarrow Sc8 \rightarrow Sc1 \rightarrow$$

Figure 6. Logic diagram of carrier swapping

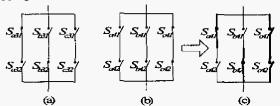

# B. Minimize the Additional Switch Operation Caused by Carrier-swapping

An additional switching operation is needed when the states of the relative two switches in a swapping operation are different. Fig.7(a) and (b) gives the states of switches in converter module 3 and 4 before a certain swapping operation. After swapping, the gate signal of module 3 is applied to module 4. Then the states of the switches in module 3 before swapping are copied to module 4, as showing in Fig.7(c). The states of switches  $S_{a4l}$ ,  $S_{b42}$ ,  $S_{c4l}$ ,  $S_{c42}$  are changed. This is the additional switching operation caused by carrier signal swapping.

Figure 7. Additional switch operation caused by control signal swapping

Then the working frequency of the power switch may be increased and the power loss will be raised. Considering this problem, swapping-time should be selected at a proper point to minimize additional switching operation caused by swapping.

After investigating the states of the switches in a four-modules converter at different M and  $\alpha$ , we can find out that at some certain time, most switches have the same states (on or off), for example, as showing in Fig. 7, the states of  $S_{b31}$  and  $S_{b41}$  are all off, it means that the states of phase B upper side switches of module 4 need not to be changed if we swap the carrier signal at this time, no additional switch operation is needed. Such time point is an optimum time point to swap the carrier. There are six positions which are the optimum time for swapping in every modulation signal period.

Studying by simulation and experiment shows that there are only 4 switches in total 24 switches need to be operated when M equal 0.8 or 1.0. When the value of M decreased, the number of the switch which needs an additional operation caused by swapping is increased to 8. The additional switch operation needed by the carrier-swapping is few.

## C. A Method to Generate the Optimum Swap Synchronous Signal

The rising edge of the swapping synchronous signal is the time point of swapping, so the rising edge of the swap synchronous signal should be selected at the optimum time point of swapping to reduce additional switch operation. For a four-modules converter working at 3 times switch frequency, the time of positive edge of swap synchronous signal can be selected as the second one of all four *ABSYabci* signal transition. Where,

ABSYabci=ABS(Yai) OR ABS(Ybi) OR ABS(Yci) ,( i=1 to 4)

ABS(Yai), ABS(Ybi) and ABS(Yci) is the absolute value of the Y signal of each phase of module i. The produce of Y signal is given in section II.

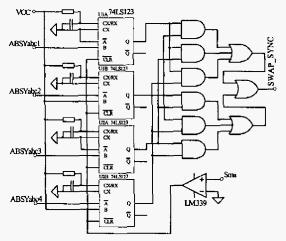

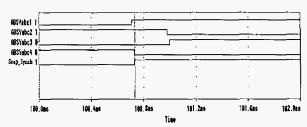

The logical circuit to produce the optimum swap synchronous signal is shown in Fig.8. Fig.9 shows that the

Figure 8. A circuit to generate swap synchronous signal which can obtain lowest additional switch operation caused by carrier swapping

Figure 9. Relationship between swap synchronous signal and ABSYabci( i=1 to 4)

time of positive edge of swap synchronous signal is the time of the second one of all four ABSYabci signal transition.

When the number of modules or the switch frequency is changed, the optimum swap time will change. The optimum time can be decided by analyzing the gate signal of each switch of each module.

### IV. EXPERIMENTS

The experiment circuit is composed eight modules. Fig.10 gives the diagram of the experimental circuit. DC reactance is 80mH, switch devices are MOSFET IRF630, serial connected with a diode IR20ETS8. The total current rate of this eight-module converter is 40 A and its total power rate is 4kW. Eight RISC embedded MCU are used to control those eight converter modules, these MCU then communicate with PC through parallel port to get the instantaneous value of M and a.

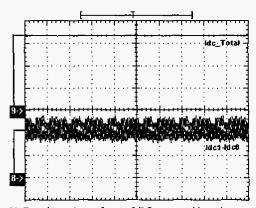

Fig.11 gives the DC current distribution with carrier swapping. The amplitude and average value of the DC current of each module are same. The individual DC current of eight modules with apparent ripple constitute a virtually ripple free DC current in the superconducting coil because the phase angle of the ripple in the DC current of each module is evenly shifted while the angle of carrier signal is evenly shifted.

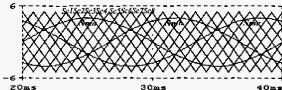

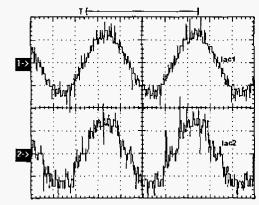

Fig. 12 shows the total AC current waveform. In the figure, waveform (1) is the AC current waveform with carrier swapping control but without individual M and  $\alpha$  adjustment of each module, waveform (2) is the AC waveform with

control of M and  $\alpha$  of each module to balance current sharing. Comparing with waveform (2), waveform (1) is improved apparently.

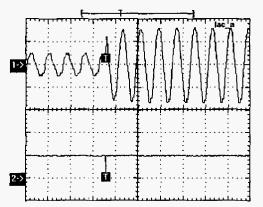

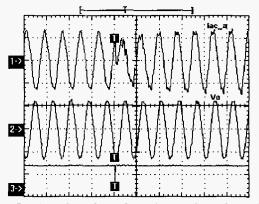

The step-up waveforms in Fig.13 and Fig.14 show that the multi-modular current source converter with carrier swapping has good dynamic response and stability. Fig.13 is the M jumping from 0.2 to 1.0, Fig.14 is α jumping form 180° to 0°. Both show the response of the multi-modular converter is fast.

Figure 10. Diagram of the experimental circuit

Figure 11, Experimental waveforms of DC current with carrier swapping. (1-8) DC current of each module. (9) Total DC current Time:100mS/div Idc1-Idc8: 200mA/div, Idc\_Total:1A/div

Figure 12. Experimental waveforms of Total AC current before the output filter. (1) Using carrier swapping to balance current sharing. (2) Using individual adjustment of M and α of each module to balance current sharing.

Time: 5mS/div I: 2 A/div

Figure 13. Experimental waveforms of the AC current for a sudden variation of M (from 0.2 to 1.0). (1)Current waveform. (2)Command signal of the variation. Time: 25mS/div I(1): 2A/div V(2):5V/div

Figure 14. Experimental waveforms of the AC current for a sudden variation of α (from 180° to 0°). (1) Current. (2) Voltage waveform as a reference. (3)Command signal of the variation.Time:25mS/div I(1): 1 A/div V(2,3): 5V/div

## V. CONCLUSION

Current un-balance caused by carrier phase-shifting is serious in a multi-modular current source converter employing phase-shifted SPWM control while carrier frequency is low. When adjusting the M and  $\alpha$  of the modulation signal of each module respectively, though the DC current sharing can be balanced, the total AC current is distorted serious. The experiments have showed that the carrier-swapping method can solve DC current unbalance without adjusting the M or  $\alpha$  of the modulation signal of each module individually. The harmonics of the AC current can be reduced comparing with the current balance control loop employing M and  $\alpha$  adjusting. The additional switch operation needed by the carrier swapping is few while adopting an optimum synchronous signal for swapping. The feature

of fast respond of this converter makes it suit to be a PCS of SMES.

#### ACKNOWLEDGMENT

The authors would like to thank the financial support of The National High Technology Research and Development Program of China (863 Program: 2002AA306331) and the project G-T177 from Research Committee of Hong Kong Polytechnic University.

#### REFERENCE

- C.-S. Hsu and W.-J. Lee "Superconducting magnetic energy storage for power system applications" *IEEE Transactions on Industry Applications*, Volume: 29 Issue: 5, Sept.-Oct. 1993 Page(s): 990 -996

- [2] V. Karasik, K. Dixon, C. Weber, B. Batchelder, G. Campbell and P. Ribeiro "SMES for power utility applications: a review of technical and cost considerations" *IEEE Transactions on Applied Superconductivity*, Volume: 9 Issue: 2 Part: 1, June 1999 Page(s): 541-546

- [3] T. Sakai, A. Kawaguchi, T. Yonemoto, "SMES system with snubber loss free type current source converter" 23rd International Conference on Industrial Electronics, Control and Instrumentation, 1997. IECON 97, Volume: 2, 9-14 Nov 1997 Page(s): 443-446 vol.2

- [4] I.J. Iglesias, J. Acero and A. Bautista "Comparative study and simulation of optimal converter topologies for SMES systems" *IEEE Transactions on Applied* Superconductivity, Volume: 5 Issue: 2 Part: 1, June 1995 Page(s): 254-257

- [5] Z.-C. Zhang and B.-T. Ooi, "Multi-modular current-source SPWM converters for a superconducting magnetic energy storage system" *IEEE Transactions on Power Electronics*, Volume: 8 Issue: 3, July 1993 Page(s): 250-256

- [6] K. Imaie, O. Tsukamoto and Y. Nagai, "Control strategies for multiple parallel current-source converters of SMES system" *IEEE Transactions on Power Electronics*, Volume: 15 Issue: 2, March 2000 Page(s): 377-385

- [7] Xu Dehong and Eisuke.Masada, "GTO PWM current converter array for SMES", Proceeding of the Chinese Society for Electrical Engineering, Vol.18, No. 2.

- [8] X. Wang and B.-T. Ooi "Unity PF current-source rectifier based on dynamic tri-logic PWM" IEEE Transactions on Power Electronics, Volume: 8 Issue: 3, July 1993 Page(s): 288-294