1

The following publication Tang, W., Zhao, J., Huang, Y., Ding, L., Li, Q., Li, J., ... & Guo, X. (2017). Bias stress stability improvement in solution-processed low-voltage organic field-effect transistors using relaxor ferroelectric polymer gate dielectric. IEEE Electron Device Letters, 38(6), 748-751 is available at https://doi.org/10.1109/LED.2017.2696987.

# Bias Stress Stability Improvement in Solution-processed Low-voltage Organic Field-effect Transistors Using Relaxor Ferroelectric Polymer Gate Dielectric

Wei Tang, Student Member, IEEE, Jiaqing Zhao, Student Member, IEEE, Yukun Huang, Li Ding, Qiaofeng Li, Jinhua Li, Peng You, Feng Yan, and Xiaojun Guo, Member, IEEE

Abstract—Low voltage organic field effect transistors (OFETs) using relaxor ferroelectric polymer poly(vinylidene fluoridetrifluoroethylene-chlorofloroethylene)

(P(VDF-TrFE-CFE)) were fabricated. The measured hysteresis loop and threshold voltage shift under negative bias stress (NBS) are opposite to that of the reference device using low-k CYTOP gate dielectric layer, in which the hysteresis and NBS induced instabilities are explained by gate bias induced charge trapping. The anomalous behaviors in the P(VDF-TrFE-CFE) OFETs are attributed to the stress-induced remnant polarization in P(VDF-TrFE-CFE), which induces additional mobile charges into the channel. By adding a thin CYTOP layer between the P(VDF-TrFE-CFE) layer and the semiconductor layer, the two effects of charge trapping and remnant polarization under gate bias are found to be neutralized with each other, resulting in low voltage OFETs of negligible hysteresis and excellent NBS stability.

*Index Terms*—organic field-effect transistor (OFET), low voltage, solution processed, high-k.

# I. INTRODUCTION

Being processed by solution or printing based approaches at low temperature, and owing excellent intrinsic mechanical flexibility, organic field-effect transistors (OFETs) will find a wide range of applications in low-cost and flexible electronics especially displays, sensors and hybrid integration systems [1-3]. However, for those envisioned practical applications, reducing the operation voltage and improving the operational stability under electrical bias becomes the major challenges. Enlarging the gate dielectric capacitance for enhanced gate

Manuscript received xxx, 2017. This work was supported by National Key R&D Program (Grant No. 2016YFB0401100), the NSFC of China (Grant No. 61674102, 61334008), Science and Technology Program of Guangdong Province, China (2015B090914003), and the Natural Science Fund for Distinguished Young Scholars of Hubei Province, China (No. 2016CFA036). (Corresponding author: Xiaojun Guo.)

- W. Tang, J. Zhao, Y. Huang, L. Ding, Q. Li, and X. Guo are with the Department of Electronic Engineering, Shanghai Jiao Tong University, Shanghai 200240, China (e-mail: x.guo@sjtu.edu.cn).

- J. Li is with the Hubei Collaborative Innovation Center for Advanced Organic Chemical Materials, School of Materials Science and Engineering, Hubei University, Wuhan 430062, China.

- P. You and F. Yan are with the Department of Applied Physics, The Hong Kong Polytechnic University, Hong Kong (e-mail: apafyan@polyu.edu.hk).

control of the channel is a widely adopted approach for low voltage OFETs. It can also be helpful in improving the current driving capability and the transconductance, and minimizing possible short-channel effects with shorter channel devices [4]. High gate capacitance can be achieved by using a ultra-thin gate dielectric layer. However, in the fabrication of OFETs over large area substrates with solution based or printing processes, this approach is not applicable due to the resulted poor device reliability and low yield. Therefore, lots of work has been carried out on using high dielectric constant (high-k) gate dielectric material for low voltage OFETs [5]. To meet the overall needs of low temperature solution processing and intrinsic mechanical flexibility of OFETs, polymer high-k dielectrics are more preferable, compared to inorganic counterparts. Among very few choices of high-k polymer dielectrics, relaxor ferroelectric polymer poly(vinylidene fluoridetrifluoroethylene-chlorofloroethylene)

(P(VDF-TrFE-CFE)) was reported to have the highest k value of about 60 [6], and has been successfully used in low-voltage OFETs based on various organic semiconductors[7-9]. However, the operational stability under bias stress with OFETs using this gate dielectric layer has not been studied., It has been reported that a negative gate bias stress (NBS) can induce a threshold voltage ( $V_{th}$ ) shift in a p-type OFET operated in inert environment [10]. The main mechanism for the NBS induced  $V_{\rm th}$  shift is attributed to be the trapping of carriers from the gate bias-induced conduction channel into less mobile localized states. Therefore,  $V_{\rm th}$  of the device normally shifts toward the negative direction [11]. In this work, we found that p-type OTFTs with the P(VDF-TrFE-CFE) high-k gate dielectric under continuous NBS shows  $V_{th}$  shift towards the positive direction., By inserting a thin CYTOP layer between the P(VDF-TrFE-CFE) layer and the semiconductor layer, we luckily found that the NBS stability as well as the overall performance of the device was significantly improved due to the synergic effect of the double-layer gate dielectric.

### II. EXPERIMENTAL

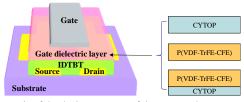

The OFETs were fabricated with a top-gate bottom-contact structure as shown in Fig. 1. The fabrication details can be

© 2017 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

found in [12]. Chromium (Cr) of 5 nm and gold (Au) of 40 nm were thermally evaporated onto pre-cleaned glass substrate through a shadow mask to define source/drain (S/D) electrodes with the channel width of 2000 µm and channel length of 120 µm. The surfaces of the S/D electrodes were treated with pentafluorobenzenethiol (PFBT) self-assembled monolayers (SAMs) to form better contacts with the organic semiconductor Donor-acceptor copolymer laver. semiconductor indacenodithiophene-benzothiadiazole (IDTBT) was deposited by spin-coating from a 5 mg/ml solution in chlorobenzene, followed by annealing at 150 °C for 30 min in nitrogen  $(N_2)$ atmosphere. A 270 nm thick P(VDF-TrFE-CFE) gate dielectric was formed by spin-coating a 40 P(VDF-TrFE-CFE) solution (56/36.5/7.5 mol%) in methyl ethyl ketone and subsequently annealing at 65 °C for 3 hours in  $N_2$  atmosphere. A reference device was fabricated using an about 900 nm thick CYTOP gate dielectric layer, deposited by spin-coating of the CYTOP solution (CTL-809M, Asahi Glass Japan) as received and annealing in vacuum at 100 °C for 30 min. The thin layer CYTOP of about 8 nm thickness inserted between the P(VDF-TrFE-CFE) layer and the IDTBT layer was formed by spin-coating a diluted CYTOP solution dissolved in its solvent CT-Solv.180 in a ratio of 1:30 (wt%). Finally, for all three type devices, 100 nm-thick aluminum (Al) gate electrodes were deposited by thermal evaporation. All the electrical characterization was carried out with a Agilent 4156C semiconductor parameter analyzer in  $N_2$  atmosphere to exclude any influence from water and oxygen in the air ambient. The capacitances were characterized with an Agilent 4294A precision impedance analyzer at 40 Hz. The measured k values of P(VDF-TrFE-CFE) and CYTOP are about 58 and 2.1, respectively.

Fig. 1. Schematic of the device structure of the top-gate bottom-contact OFET to be studied in this work using different gate dielectric layers: single layer CYTOP, single layer relaxor ferroelectric terpolymer P(VDF-TrFE-CFE), and P(VDF-TrFE-CFE)/CYTOP bilayer.

## III. RESULTS AND DISCUSSIONS

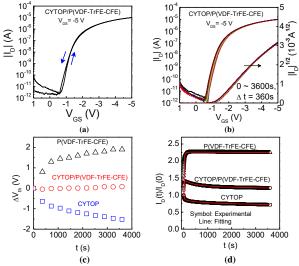

Fig. 2 (a) and (b) show the measured forward and reverse transfer curves ( $I_D$ - $V_{GS}$ ) for the fabricated OFETs using CYTOP and P(VDF-TrFE-CFE) as the gate dielectric layer, respectively. Compared to the CYTOP device with subthreshold swing (SS) of 2.1 V/dec, the P(VDF-TrFE-CFE) one has much smaller SS of 150 mV/decade attributed to the large gate dielectric capacitance of 190 nF/cm<sup>2</sup>. The mobility reduction from about 1.3 cm<sup>2</sup>/V·s for the CYTOP device to 0.3 cm<sup>2</sup>/V·s for the P(VDF-TrFE-CFE) one is caused by enhanced carrier localization due to the random dipoles at the surface of the high-k gate dielectric, which has been discussed previously [12-13].

For the CYTOP device, the hysteresis loop in Fig. 2(a) is

along the clockwise direction, while for the P(VDF-TrFE-CFE) device, it is along the anti-clockwise direction (Fig. 2(b)). The hysteresis windows for both devices are about 0.5 V as indicated. The  $I_{\rm D}$ - $V_{\rm GS}$  curves measured at different time under continuous NBS for the two type devices are given in Fig. 2(c) and (d), respectively. It can be seen that the  $I_{\rm D}$ - $V_{\rm GS}$  curve of the CYTOP device shifts towards the negative direction, and differently, the  $I_{\rm D}$ - $V_{\rm GS}$  curve of the P(VDF-TrFE-CFE) one shifts towards the positive direction. The hysteresis and NBS instability behaviors of the CYTOP device can be explained by gate bias induced trapping of positive charges into localized states [14], which, however, is obviously not applicable to the P(VDF-TrFE-CFE) device.

Fig. 2. (a) The measured forward and reverse transfer curves  $(I_{\rm D}\text{-}V_{\rm GS})$  for the OFET with CYTOP gate dielectric layer. (b) The measured forward and reverse  $I_{\rm D}\text{-}V_{\rm GS}$  for the OFET with P(VDF-TrFE-CFE) gate dielectric layer. (c)  $I_{\rm D}\text{-}V_{\rm GS}$  curves measured at different time under negative bias stress (NBS) at  $V_{\rm GS}$ = -60 V,  $V_{\rm DS}$ = -5 V for the CYTOP OFET. (d)  $I_{\rm D}\text{-}V_{\rm GS}$  curves measured at different time during NBS at  $V_{\rm GS}$ = -5 V,  $V_{\rm DS}$ = -0.5 V for the P(VDF-TrFE-CFE) OFET.

Such a high k value of 58 with P(VDF-TrFE-CFE) is formed by large dipole moment of the monomer unit, high dipole density and strong dipolar coupling between the polarization entities in the VDF structure [7]. Although its polarization induced hysteresis is much reduced by introducing CFE units to prohibit the formation of large polarization domains, the remnant polarization cannot be completely eliminated [6, 7]. Previous work has also provided direct experimental evidence of electric field induced polarization in the ferroelectric relaxor terpolymer [15, 16]. Therefore, when P(VDF-TrFE-CFE) directly interfaces the organic semiconductor layer, dipole electric field caused by this remnant polarization under gate bias will induce additional mobile charges in the channel [17]. As a result, it leads to higher channel current, and thus the anti-clockwise hysteresis loop and also positive shift of  $I_D$ - $V_{GS}$  curve under NBS.

For the CYTOP/P(VDF-TrFE-CFE) OFET, both the hysteresis and NBS induced  $I_D$ - $V_{GS}$  shift become negligible as shown in Fig. 3(a) and (b), respectively. The device can still be operated below 5 V with a gate dielectric capacitance of 104 nF/cm<sup>2</sup>, despite of a slightly larger SS of 158 mV/dec. The

mobility is about 1.3 cm<sup>2</sup>/V·s, similar to that of the CYTOP device. The extracted threshold voltage  $(V_{th})$  shifts over time under NBS for the three type devices are compared in Fig. 3(c).  $V_{\rm th}$  of the P(VDF-TrFE-CFE) device and the CYTOP one shifts towards the opposite directions due to the different mechanisms as discussed above. The CYTOP/P(VDF-TrFE-CFE) device has much improved bias stress stability with  $V_{\rm th}$  less than 0.08 V after 3600 s. These results indicate that in the CYTOP/P(VDF-TrFE-CFE) device the two effects of charge trapping and remnant polarization under gate bias are neutralized with each other. To further prove this, the drain current evolution over time for the three devices under continuous NBS were plotted in Fig.3(d). It can be seen that the current decay with the CYTOP device fits very well with the following equation (1) in a stretched exponential law standing for charge trapping effect [18].

$$I_{\rm D}({\rm t}) = I_{\rm D}(0) exp \left[ -\left(\frac{t}{\tau_d}\right)^{\beta} \right] \tag{1}$$

where  $I_D(0)$  is the initial drain current,  $\tau_d$  the characteristic time for charge trapping, and  $\beta$  the dispersion parameter. In contrast to the CYTOP device, the drain current for the P(VDF-TrFE-CFE) device increases rapidly in the beginning and then reached a maximum value, which agrees well with the following equation (2) describing the current evolution over time under gate bias due to polarization effect [18]

$$I_{\rm D}(t) = I_{\rm D}(0) + \Delta I_{\rm D}(\infty) \left\{ 1 - exp \left[ -\left(\frac{t}{\tau_p}\right)^{\alpha} \right] \right\}$$

(2)

where  $\Delta I_D(\infty)$  is the constant current parameter,  $\tau_p$  the characteristic time for polarization, and  $\alpha$  the dispersion parameter.

Fig. 3. (a) The measured forward and reverse transfer curves  $(I_{\rm D}\text{-}V_{\rm GS})$  for the fabricated OFET with CYTOP/P(VDF-TrFE-CFE) bilayer gate dielectric. (b)  $I_{\rm D}\text{-}V_{\rm GS}$  curves measured at different time under negative bias stress (NBS) at  $V_{\rm GS}$ = -5V,  $V_{\rm DS}$ = -0.5 V for the bilayer OFET. (c) Comparisons of the extracted threshold voltage ( $V_{\rm th}$ ) shift over time under NBS for the three type OFETs with different gate dielectrics. (d) Comparisons of the drain current evolution over time for the three devices under continuous NBS.

The CYTOP/P(VDF-TrFE-CFE) device exhibits a current change which can be fit well using the following equation (3) as a sum of equation (1) and (2). The results prove that the

combined effects of charge trapping and remnant polarization on improving the bias stress stabilities of the devices.

$$I_{\rm D}(t) = \Delta I_{\rm D}(\infty) \left\{ 1 - exp \left[ -\left(\frac{t}{\tau_{\rm D}}\right)^{\alpha} \right] \right\} + I_{\rm D}(0) exp \left[ -\left(\frac{t}{\tau_{\rm d}}\right)^{\beta} \right]$$

(3)

# IV. CONCLUSIONS

The fabricated low voltage OFETs using high-k P(VDF-TrFE-CFE) gate dielectric presents hysteresis loop and  $V_{\rm th}$  shift under NBS opposite to that of the reference device with low-k CYTOP gate dielectric layer. The physical mechanism is considered to be that the dipole electric field from remnant polarization in P(VDF-TrFE-CFE) induces additional mobile charges into the channel. By adding a thin CYTOP layer between the P(VDF-TrFE-CFE) layer and the semiconductor layer, the two effects of charge trapping and remnant polarization under gate bias are found to be neutralized with each other, resulting in low voltage OFETs of negligible hysteresis and excellent NBS stability. This work provides a solution for developing low voltage and stable OFETs by using the high-k relaxor ferroelectric polymer as the gate dielectric layer.

### REFERENCES

- [1]M. Mizukami, S. Oku, S.-I. Cho, M. Tatetsu, M. Abiko, M. Mamada, T. Sakanoue, Y. Suzuri, J. Kido, and S. Tokito, "A solution-processed organic thin-film transistor backplane for flexible multiphoton emission organic light-emitting diode displays," *IEEE Electron Device Lett.*, vol. 36, no. 8, pp. 841-843, Aug. 2015, doi: 10.1109/LED.2015.2443184.

- [2] A. C. Arias, J. D. MacKenzie, I. McCulloch, J. Rivnay, and A. Salleo, "Materials and applications for large area electronics: solution-based approaches," *Chem. Rev.*, vol. 110, no. 1, pp. 3-24, Jan. 2010, doi: 10.1021/cr900150b.

- [3]W. Tang, C. Jiang, Q. Li, W. Hu, L. Feng, Y. Huang, J. Zhao, S. Chen, and X. Guo, "Low-voltage pH sensor tag based on all solution processed organic field-effect transistor," *IEEE Electron Device Lett.*, vol. 37, no. 8, pp. 1002-1005, Jun. 2016, doi: 10.1109/LED.2016.2580565.

- [4] X. Guo, R. Sporea, J. Shannon, and S. Silva, "Down-scaling of thin-film transistors: opportunities and design challenges," *ECS Trans.*, vol. 22, pp. 227-238, 2009, doi: 10.1149/1.3152980.

- [5]R. P. Ortiz, A. Facchetti, and T. J. Marks, "High-k organic, inorganic, and hybrid dielectrics for low-voltage organic field-effect transistors," *Chem. Rev.*, vol. 110, no. 1, pp. 205-239, Oct. 2009, doi: 10.1021/cr9001275.

- [6]J. Li, Z. Sun, and F. Yan, "Solution processable low-voltage organic thin film transistors with high-k relaxor ferroelectric polymer as gate insulator," Adv. Mater., vol. 24, no. 1, pp. 88-93, Jan. 2012, doi: 10.1002/adma.201103542.

- [7]S. Wu, M. Shao, Q. Burlingame, X. Chen, M. Lin, K. Xiao, and Q. M. Zhang, "A high-K ferroelectric relaxor terpolymer as a gate dielectric for organic thin film transistors," *Appl. Phys. Lett.*, vol. 102, no. 1, p. 013301, Jan. 2013, doi: 10.1063/1.4773186.

- [8]B. Nketia-Yawson, H.-S. Lee, D. Seo, Y. Yoon, W.-T. Park, K. Kwak, H. J. Son, B. Kim, and Y.-Y. Noh, "A highly planar fluorinated benzothiadiazole-based conjugated polymer for high-performance organic thin-film transistors," *Adv. Mater.*, vol. 27, no. 19, pp. 3045-3052, May 2015, doi: 10.1002/adma.201500233.

- [9]L. Xiang, J. Ying, W. Wang, and W. Xie, "High mobility n-channel organic field-effect transistor based a tetratetracontane interfacial layer on gate dielectrics," *IEEE Electron Device Lett.*, vol. 37, no. 12, pp. 1632-1635, Dec. 2016, doi: 10.1109/led.2016.2616517.

- [10]W. H. Lee, H. H. Choi, D. H. Kim, and K. Cho, "25th anniversary article: microstructure dependent bias stability of organic transistors," *Adv. Mater.*, vol. 26, no. 11, pp. 1660-1680, Mar. 2014, doi: 10.1002/adma.201304665.

- [11]H. Sirringhaus, "Reliability of organic field-effect transistors," *Adv. Mater.*, vol. 21, no. 38-39, pp. 3859-3873, Oct. 2009, doi: 10.1002/adma.200901136.

- [12]W. Tang, J. Li, J. Zhao, W. Zhang, F. Yan, and X. Guo, "High-performance solution-processed low-voltage polymer thin-film transistors with

- low-k/high-k bilayer gate dielectric," *IEEE Electron Device Lett.*, vol. 36, no. 9, pp. 950-952, Sep. 2015, doi: 10.1109/LED.2015.2462833.

- [13]J. Lee, J. W. Chung, G. Yoon, M. H. Lee, D. H. Kim, J. Park, J.-K. Lee, and M. S. Kang, "Influence of dielectric layers on charge transport through diketopyrrolopyrrole-containing polymer films: dielectric polarizability vs capacitance," ACS Appl. Mater. Interfaces, vol. 8, no. 44, pp. 30344-30350, Nov. 2016, doi: 10.1021/acsami.6b09993.

- [14]W. Tang, J. Zhao, L. Feng, P. Yu, W. Zhang, and X. Guo, "Top-gate dry-etching patterned polymer thin-film transistors with a protective layer on top of the channel," *IEEE Electron Device Lett.*, vol. 36, no. 1, pp. 59-61, Jan. 2015, doi: 10.1109/LED.2014.2367012.

- [15] S. Zhang, B. Chu, B. Neese, K. Ren, X. Zhou, and Q. M. Zhang, "Direct spectroscopic evidence of field-induced solid-state chain conformation transformation in a ferroelectric relaxor polymer," *J. Appl. Phys.*, vol. 99, no. 4, p. 044107, 2006, doi: doi:http://dx.doi.org/10.1063/1.2169659.

- [16]X. Chen, L. Liu, S.-Z. Liu, Y.-S. Cui, X.-Z. Chen, H.-X. Ge, and Q.-D. Shen, "P(VDF-TrFE-CFE) terpolymer thin-film for high performance nonvolatile memory," *Appl. Phys. Lett.*, vol. 102, no. 6, p. 063103, Feb. 2013.

- [17]M. Egginger, S. Bauer, R. Schwödiauer, H. Neugebauer, and N. Sariciftci, "Current versus gate voltage hysteresis in organic field effect transistors," *Monatsh. Chem.*, vol. 140, no. 7, pp. 735-750, Jul. 2009, doi: 10.1007/s00706-009-0149-z.

- [18]N. V. V. Subbarao, M. Gedda, P. K. Iyer, and D. K. Goswami, "Enhanced environmental stability induced by effective polarization of a polar dielectric layer in a trilayer dielectric system of organic field-effect transistors: a quantitative study," ACS Appl. Mater. Interfaces, vol. 7, no. 3, pp. 1915-1924, Dec. 2015, doi: 10.1021/am507636k.

E-mail list

terry\_tang@sjtu.edu.cn

jinhua\_li@hubu.edu.cn

j.zhao@sjtu.edu.cn

wjh1056@sjtu.edu.cn

dl1992720@sjtu.edu.cn

jerry0128@gmail.com

jnyp1029@126.com

zhangweimin@gxun.edu.cn

feng.yan@polyu.edu.hk

x.guo@sjtu.edu.cn